《半導体の後工程を学ぶ④》キーワードは”HI”|SiPの技術はさらなる高度化・高密度化へ

![]()

前回まで一つのチップをパッケージに組み立てる工程について復習してきましたが、その中で説明したμバンプを用いたフリップチップ技術やFO(Fan-Out)技術が “SiP“につながっています。

1.FOプロセス

下はFOプロセスの応用例です。

図に示したように、A、B、C、Dの四つの種類のICチップをキャリアに精密に配置し、樹脂でモールドしたのちウェハプロセス装置を使ってRDL(再配線層)を形成し、半田ボール搭載まで行ってからスクライブライン(図の白線)に沿ってダイシングすれば、2.xDのSiPが実現できます。

![]()

【図1 2.xDのSiP】

これはChip-1stプロセスですが、キャリア上に再配線層をあらかじめ形成(RDL-1st)し、そこにA、B、C、Dの四つの種類のICをフリップチップボンディングして樹脂モールドしても同様の結果が得られます。

2.TSV(Through Silicon Via)とは

もう一つの重要課題である3D SiPを実現するためには、さらに「TSV」と呼ばれる技術が必要ですので、これについて説明します。

「TSV」(Through Silicon Via)とは、Si基板を貫通する垂直配線のことです。

“Via”は「経由して」という意味で、この場合はビアホール(via hole)、すなわち穴を経由してということを示しています。ビアホール自体は、半導体の多層配線における上下配線間の接続、積層プリント基板の層間の接続などにも使われています。

![]()

【図2 TSV_ICチップ】

TSVのメリット

例えば図2のように二つのICチップを積層する場合、ICチップのSi基板部分を貫通する穴を銅などの金属で埋めたTSVを用いれば、各ICチップをワイヤボンディングでパッケージに接続する場合に比べて小さな面積で、かつ配線距離も短く(すなわち、より速い信号伝達速度で、より低い消費電力で)接続することができます。

さらに、ワイヤボンディングの場合、チップ周辺部にボンディングパッドを設ける必要があること、ワイヤ同士が干渉しないようにしなければならないことから接続数は制限されますが、TSVの場合、チップ中央部からでも真下に接続することができますので、接続数を大幅に増やすことができるのです。

ここではICチップを2段に積んだだけですが、原理的には何段でも積むことができ、これはまさに3D SiPそのものです。

TSVのデメリット

技術的には、前工程でドライエチングなどの方法で細長い穴をシリコン基板にあけ、さらにその細長い穴を銅などの金属で埋めること、後工程で上下のTSVを非常に小さなバンプ(μBump:マイクロバンプ)で接続することが必要になります。

このように、プロセス技術上の難易度が上がることに加え、埋め込んだ金属とシリコンの熱膨張率の差で応力がかかりトランジスタの性能が変化するため、TSV周辺にトランジスタを置かないようにするなどのデバイス配置上の配慮も必要で、なんでもかんでも3Dにすれば良いというわけではありません。

3.”2.xD”と”3D”を組み合わせたSiP

そこで下図のように、2.xDと3Dを組み合わせたSiPも提案されています。

![]()

【図3 2.xDと3Dを組み合わせたSiP】

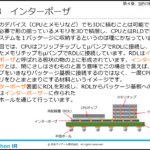

異種のデバイス(CPUとメモリなど)でも3Dに積むことは可能ですが、量が必要で形の揃っているメモリを3Dで積層して、CPUとはRLDで繋いでシステムを1パッケージに収納するというのは理にかなっています。

この図では、CPUはフリップチップしてμバンプでRDLに接続し、積層したメモリチップもμバンプでRDLに接続しています。RDLは「インターポーザ」と呼ばれる板状の物の上に形成されています。

インターポーザの役割

「インターポーザ」とは、間にさしはさむものと言う意味で、この場合で言えば、チップをいきなりパッケージ基板に接続するのではなく、一度CPUとメモリをひとまとまりにする材料というイメージです。インターポーザ表面にRDLを形成し、RDLからパッケージ基板への接続はインターポーザに作られたビアホールを通じて行っています。

インターポーザは、このように物理的にチップとパッケージ基板の間に介在するだけでなく、配線ピッチのギャップを埋める役割も持っています。

前工程で形成される、デバイスチップの最小線幅はナノメータレベルで、チップの配線層の最上層でも最大で1~2μm程度です。一方、パッケージ基板の配線幅は数μm~数十μmです。

そこで、各デバイスチップ間を最適な線幅でかつ短距離で接続し、1μm程度から10μm程度の配線幅の範囲をカバーするのがインターポーザ―上に形成されたRDLです。

インターポーザの材質はシリコン、ガラス、有機材料などがあり、シリコンは半導体前工程が使えるのでプロセスしやすい、デバイスチップと熱膨張率(CTE:Coefficient of Thermal Expansion)が同じなので動作時の熱によるひずみが入りにくいなどのメリットがありますが、高価であることがネックです。

4.熾烈な技術開発競争が続く”HI”

今後のSiPはここまでに紹介した技術を組み合わせ、さらに高度化して高密度化をめざします。

CPUやメモリとはプロセスが全く異なる高周波デバイスや光デバイスなども一つのパッケージへの集積が可能になりつつあり、このように製造技術や機能、大きさが異なる各種のデバイスチップを一つのパッケージに集積することを「ヘテロジニアスインテグレーション」(HI: Heterogeneous Integration)とも呼んでいます。

今回紹介した、ABCD四つのチップを樹脂で固めたSiPもHIの一つですし、積層したメモリとCPUをインターポーザ―で接続した例もHIです。さらに複雑なHIについては、今まさに各社が技術開発競争しているところで、百花繚乱の状態になっています。

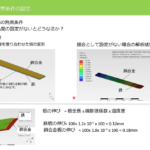

さて、連載コラムの終わりに、「半導体開発は後工程,パッケージ技術が主役の時代へ」の回で紹介した、経済産業省から出された半導体戦略で示された図をもう一度見てみましょう。

わかりやすくするために、少し手を加えています。朱字は半導体戦略の中で、開発ターゲットとしてあげているものです。

![]()

【図4 HIと開発ターゲット】

※画像引用:経済産業省「半導体戦略(概略)」

URL: https://www.meti.go.jp/press/2021/06/20210604008/20210603008-4.pdf

SoC(System on Chip)/SoIC(System on Integrated Chips)やHBM(High Bandwidth Memory:TSV技術を用いて積層したメモリ)をμバンプでシリコンインターポーザに形成されたRDLに接続し、シリコンインターポーザからはTSVとバンプで多層のパッケージ基板に繋がり、パッケージ基板から半田ボールでプリント基板に接続されているのがわかります。まさに”HI”です。

(アイアール技術者教育研究所 H・N)

- 第1回: 半導体開発は後工程,パッケージ技術が主役の時代へ

- 第2回: SoCとSiPを比較して解説|SiPのメリット・課題は?

- 第3回: 半導体パッケージ技術の基本[リードフレーム/BGA/WLP(WLCSP) ]

- 第4回: キーワードは”HI”|SiPの技術はさらなる高度化・高密度化へ