《半導体の後工程を学ぶ①》半導体開発は後工程,パッケージ技術が主役の時代へ

![]()

今、半導体の後工程が大きな注目を集めています。

これまでは、一つの半導体チップの中にできるだけ沢山のトランジスタを集積するという前工程の微細化を競ってきましたが、それも徐々に限界に達しました。現在の最先端の半導体技術開発は、複数の半導体チップをコンパクトにパッケージに組み込むという、後工程技術の進化によって高集積化を継続することにも力を入れています。

このコラムでは、半導体についてなんとなくは知っているけれど、後工程やパッケージのことはよくわからないという方のために、数回に分けて半導体パッケージの最新技術の状況を紹介します。

1.半導体製造プロセスの後工程とは?

半導体製造プロセスは、大きく二つの工程に分かれます。「前工程」と「後工程」です。

前工程は、シリコンウェハに回路を形成するまでの工程です。「クリーンルーム」と呼ばれる、空気中のゴミを極限まで減らした部屋の中で行われます。

後工程は、回路が形成されたシリコンウェハを半導体チップに切り出してパッケージに入れ、実際のIC・LSIとして出荷するまでの工程です。黒い物体からゲジゲジのような足が出ているIC・LSIの写真をよく見かけますが、これらは後工程で加工されたものです。

![]()

【図1 半導体製造プロセスの前工程と後工程】

2.More Than Moore

従来、半導体LSIの高性能化は、一つのチップにトランジスタをできるだけたくさん集積することで実現されてきたため、技術競争は長らく前工程における微細化・高集積化技術を中心に行われてきました。

そして微細化技術は、トランジスタの集積密度が2年で2倍になるという「ムーアの法則」(Mooreʼs Low)*1)に沿う形で進化してきました。

しかし近年、前工程における微細化が技術的にもコスト的にも限界に近付いているのに対し、半導体LSIに対する高機能化・多機能化の要求は留まるところを知りません。

そこで現在の最先端の半導体技術開発は、前工程のみならず、後工程でのパッケージ技術を進化させることで高集積化を継続し、半導体LSIの高機能化・多機能化の要求に応えるという方向にも向かっています。

前工程のさらなる高度化を”More Moore”と呼ぶのに対して、後工程の高度化を”More Than Moore”と呼んでいます。

具体的には次回以降に説明しますが、複数のICチップ(チップレット:Chiplet *2))を一つのパッケージにコンパクトに集積する、様々な方法が開発されています。すなわち、最近では後工程、とりわけパッケージ技術の重要度が非常に高まってきているということです。

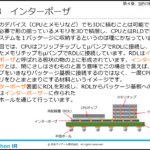

この動きは、2021年6月に経済産業省から出された「半導体戦略」*3)で、『先端半導体製造技術の共同開発とファウンドリの国内立地』が施策として打ち出され、その中で主な取組・施策として、「3D化プロセス技術開発プロジェクト(More than Moore): 日本の製造装置・素材産業等と海外の先端ファウンドリとの連携による先端ロジック半導体の製造技術共同開発(3D化パッケージプロセス;ヘテロジニアスインテグレーション「チップレット」)。メモリやセンサの三次元積層技術開発支援」とうたわれていることに繋がっています。

![]()

【図2 経済産業省 資料「半導体戦略」*3)より】

実際、台湾のファウンドリであるTSMCが、つくばで新会社「TSMCジャパン3DIC研究開発センター」を開所したのは記憶に新しいところです。

さらに、2022年12月14日から16日にかけて開催された「SEMICON Japan 2022」と併せて、後工程技術に特化した専門展示会「Advanced Packaging and Chiplet Summit(APCS)」の第1回が同時開催されたのも、半導体業界の世界的な潮流を象徴しています。

3.後工程での集積化技術[SiP、チップレット]

さて、後工程による集積化とはどのようなものであるか、スマートフォンに搭載されている「モバイルAP」(Application Processor)という半導体を例に、前工程による集積化と比較して少し詳しく見てみましょう。

モバイルAPは、スマートフォンの頭脳の役割を担い、CPU(Central Processing Unit)、GPU(Graphics Processing Unit)、DSP(Digital Signal Processor)、DRAM(Dynamic Random Access Memory)、MODEM(Modulator Demodulator)などを一つに集積したもので、これらの機能を前工程で一つの半導体チップ上に実現したのが「SoC」(System on Chip)技術です。

一方、CPUやDRAMなどの個別の機能を持った半導体チップを別々の前工程で作り、パッケージの中で集積(配線)してモバイルAPを作ることもできます。これを「SiP」(System in Package)と呼びます。また、SiPを構成する各々の半導体チップのことを「チップレット」(Chiplet)と呼びますが、これはSoCの半導体チップと比べて面積が小さいチップという意味です。

SoCは、非常に短い距離でデバイス間を接続できるだけでなく、後工程が単純になるというメリットがありますが、一つのチップの面積が大きくなること、異種の構造、プロセス(CMOS、DRAM等)を一つのウェハ上で実現しなければならないことなど、高性能化、大規模化に向けては様々な課題も抱えています。

次回は、SoCとSiPで同じ機能を持った半導体を実現した場合に、どのような違いがあるかを解説します。

(アイアール技術者教育研究所 H・N)

*1):ムーアの法則:

ゴードン・ムーア氏が1965年のElectronics誌で発表した「半導体回路の集積密度は1.5~2年で2倍になる」とする経験則。半導体回路の線幅微細化の進展をよりどころとしているが、近年技術的な限界が近づいているとされる。

*2):Chiplet:

小さなチップ、すなわち従来1チップに集積していた大きな回路を、例えば機能ごとに小さな回路に分けたチップのこと。さらに、これらの小さなチップを再配線層で繋いで1パッケージに収める技術をいう。

*3):半導体戦略(概略):

経済産業省、 https://www.meti.go.jp/press/2021/06/20210604008/20210603008-4.pdf

- 第1回:半導体開発は後工程,パッケージ技術が主役の時代へ

- 第2回: SoCとSiPを比較して解説|SiPのメリット・課題は?

- 第3回: 半導体パッケージ技術の基本[リードフレーム/BGA/WLP(WLCSP) ]

- 第4回: キーワードは”HI”|SiPの技術はさらなる高度化・高密度化へ