《半導体の後工程を学ぶ②》SoCとSiPを比較して解説|SiPのメリット・課題は?

1.SoCとSiPの比較(メリット・デメリット)

当連載の前回の記事では、同じ機能を持った半導体を、1チップで実現するか(SoC: System on Chip)、複数のチップ(Chiplet)を一つのパッケージに組み立てて実現するか(SiP: System in Package)の二つの方法があることを説明しました。

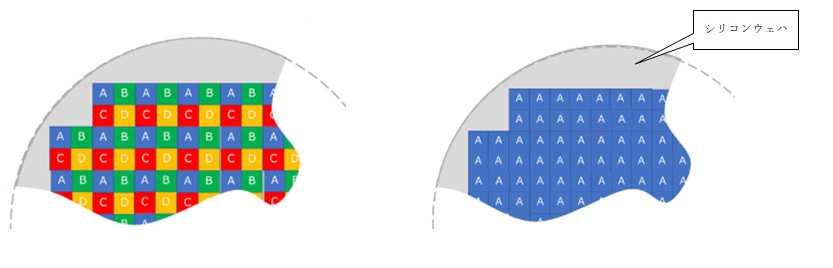

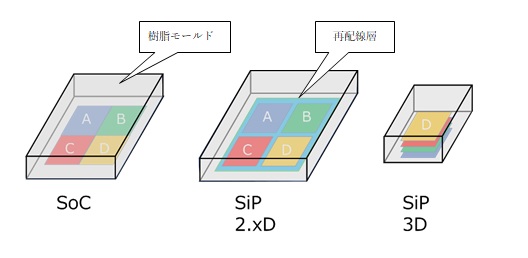

今回はもう少し具体的なイメージを持っていただくために、A、B、C、Dの四つの機能からなるシステムを一つのチップに集積するSoCと、A、B、C、Dを別々のチップ(Chiplet)で作りパッケージで集積したSiPを比較してみましょう。簡単のためにA、B、C、Dは各々同じ面積を持つものとします(図1参照)。

【図1 SoC(左)とSiP(右)のイメージ】

図1で、左はABCDを1チップとしてプロセスするのに対し、右は面積が四分の一のAのみを並べてプロセスを行います。B、C、Dについても各々別のウェハでプロセスします。

SoCのデメリット

1枚のシリコンウェハにSoCは100個並べられるとします。つまりA(あるいはB、C、D)だけなら400個並べられることになります。

また、シリコンウェハ上の10か所で何らかのプロセス異常が発生(例えばパーティクルが載ってパターン異常が起こる)し、その場所のチップは不良になるとします。不良チップは、前工程の最後に行われるプローブ検査で検出でき、パッケージに組み立てる時には不良でないとわかっているチップ(known good die: KGD)のみが使われます。

SoC(ABCD)を4枚プロセスすると、KGDは90×4=360個得られます。

A、B、C、Dを1枚ずつ(計4枚)プロセスするとそれぞれ390個のKGDが得られます。

この場合、後工程の組立歩留まりが360/390(~92%)より良ければSiPの方が歩留まりは良くなる計算です。つまり大面積チップは歩留まり的には不利ということです。

さらに、SoCでは、例えばCMOSとDRAMではウェハプロセスのキーになるプロセスが異なるので、同一ウェハに作りこむのは技術的に難易度が高いこと、最もプロセス歩留まりが悪い機能によって歩留まりが決まってしまうことなどから、プロセス歩留まりは、ゴミが載ると言った単純なモデルよりさらに悪くなります。

また、特定の用途に新たにSoCを開発するのには、パターン設計、プロセス設計共に時間がかかる、ABCDのうちどれか一つに変更を加えるだけでプロセス全体に影響が及ぶなどの問題も、SoCが高機能化するほど顕在化してきます。

SiPのメリット

一方、面積が小さいチップならウェハを大口径化するメリットはあまりなく、むしろ償却が終わった小口径のプロセスラインで安く作ることができる、ABCDすべての機能に最先端のプロセスが必要ではない、ABCDいずれかだけの設計変更も比較的容易など、SiPのメリットは沢山あります。

ここまで、SoCの悪いところだけを拾い上げるような説明になってしまいましたが、半導体前工程は、高いプロセス歩留を維持したまま線幅ナノメータレベルを達成する等、これらの問題をものともしないような素晴らしい技術発展を遂げてきました。それが最近になって限界が見えてきた、ということなのです。

2.SiPの課題

SiPにも解決しなければならない課題は沢山あります。

下の図2には、先ほどの四つの機能からなるシステムを、

- SoCとしてパッケージしたもの

- 四つのチップを平面的に並べ再配線層(RDL: Re-Distribution Layer)で各チップ間を電気的に繋いだもの(2.xD)*1)

- 四つのチップを積み重ねて縦方向に電気的に接続したもの(3D)

をイメージ的に示しています。

【図2 SoC、2.xD、3Dのイメージ】

2.xDでは、SoC並みの面積で四つのチップを電気的に繋ぐRDLをどのようなプロセスで実現するかが課題になります。

3Dでは、まさにチップ間を縦方向に電気的につなぐにはどのような方法を取れば最適かが課題で、これが実現できればパッケージの平面積を大幅に小さくできます。

このようにSiPでは、1チップのみをパッケージに組み立てる場合には使わなかった技術も新たに開発する必要があり、半導体製造各社がしのぎを削っています。

これらの新技術を説明する前に、まずは従来から行っている、前工程を終了したウェハから切り出して一つのチップだけをパッケージに組み立てる後工程について、次回のコラム「半導体パッケージ技術の基本」でおさらいしておきましょう。これは、一つのチップをできるだけコンパクトにパッケージに組み立てるための技術開発の延長にSiP技術があるからです。

パッケージとしては、メタルパッケージ、セラミックパッケージもありますが、これらは主として個別トランジスタなどのディスクリート半導体に用いられ、ICの場合には圧倒的に樹脂モールドが多いので樹脂モールドタイプを想定して話を進めることにします。

(アイアール技術者教育研究所 H・N)

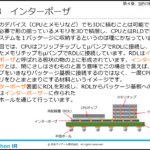

*1):2.xD

2.xDとは、チップレットを縦方向に積層した3次元実装(3D)に対し、インターポーザと呼ばれる層に高密度の再配線層(RDL)を設け、再配線層上に平面的に並べられたチップレット間を電気的に接続する実装方法。2.xD のxは、インターポーザの材質を表し、シリコンを用いた場合5(2.5D)、樹脂を用いた場合1(2.1D)と表す。

【連載コラム】「半導体の後工程を学ぶ」(全4回)

- 第1回: 半導体開発は後工程,パッケージ技術が主役の時代へ

- 第2回: SoCとSiPを比較して解説|SiPのメリット・課題は?

- 第3回: 半導体パッケージ技術の基本[リードフレーム/BGA/WLP(WLCSP) ]

- 第4回: キーワードは”HI”|SiPの技術はさらなる高度化・高密度化へ