順序回路とは?フリップフロップの種類と同期の方法を学ぶ

デジタル回路のうち、内部に記憶回路と同期回路を備え、入力信号の組み合わせだけで出力が決まらない論理回路を「順序回路」と呼びます。

「順序回路」は、現在の入力に加えて、過去の入力により出力を決定する論理回路です。これは「組み合わせ回路」ではできないことです。

では、「順序回路」が、過去の入力を現在の出力に反映させるために必要とするものは何でしょうか?

それは、過去の入力を記憶するということです。この記憶の機能を実現するものを「フリップフロップ」と呼びます。今回は、フリップフロップの基本を解説します。

1.フリップフロップの基礎知識

フリップフロップは、構造と機能によってRS型、JK型、D型、T型などの種類があります。

それぞれのタイプについて説明します。

(1)RSフリップフロップ

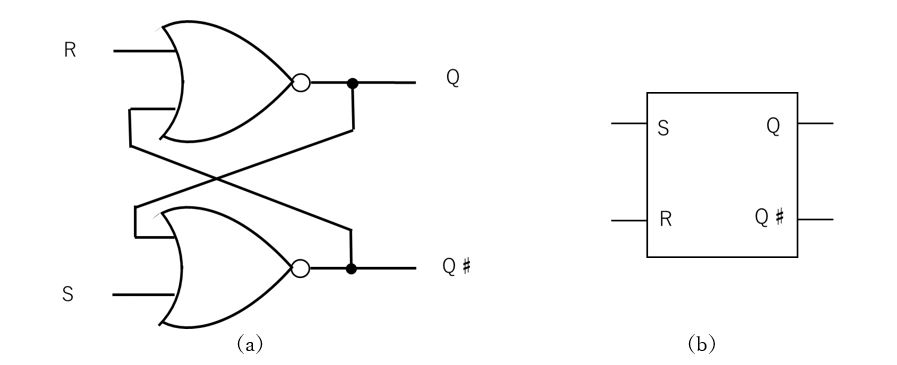

図1にNOR素子を用いたRSフリップフロップの論理回路図(a)と図記号(b)を示します。

Rはリセット入力、Sはセット入力、Qは出力、Q#は、Qの反転出力とします。

「RSフリップフロップ」とは、R(リセット)とS(セット)があるフリップフロップという意味となります

【図1 RSフリップフロップの論理回路図と図記号】

図1(a)の論理について、順に見ていきましょう。

まず、S=1、R=0を入力すると、それ以前のQ、Q#の論理値に関係なく、Q=1、Q#=0となります。これを「セット」といいます。

同様に、S=0、R=1の時は、Q=0、Q#=1となり、これを「リセット」といいます。

S=R=0の時は、この入力が入る以前のQ、Q#の論理値がそのまま保たれます。

すなわち、セットしてからS=R=0にすれば、Qは1のままであり、リセットしてからS=R=0にすれば、Qは0のままになります。

このように、RSフリップフロップは、記憶素子として働き、出力は現在の入力のみでは決まらず、過去の入力にも依存します。

S=R=1の時には、Q=Q#=0となりますが、この状態からS=R=0にすると、回路の僅かな不平衡によってどちらの状態も取りうるので、値を予測することができません。

このような入力の組み合わせは用いてはならず、「禁止入力」と呼ばれます。

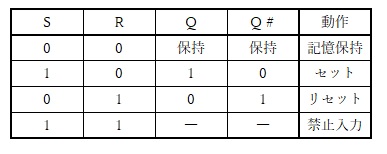

図2にRSフリップフロップの真理値表を示します。

【図2 RSフリップフロップの真理値表】

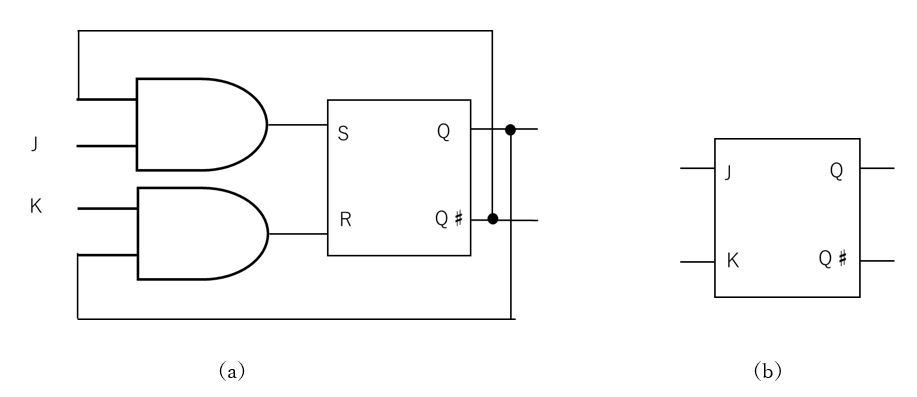

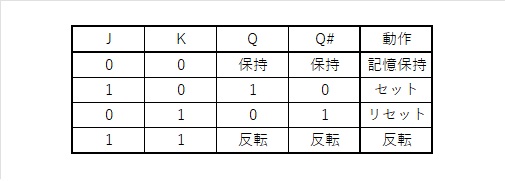

(2)JKフリップフロップ

RSフリップフロップには、禁止入力がありましたが、禁止入力を別の動作(反転させる) をするように機能を変更したものが「JKフリップフロップ」となります。

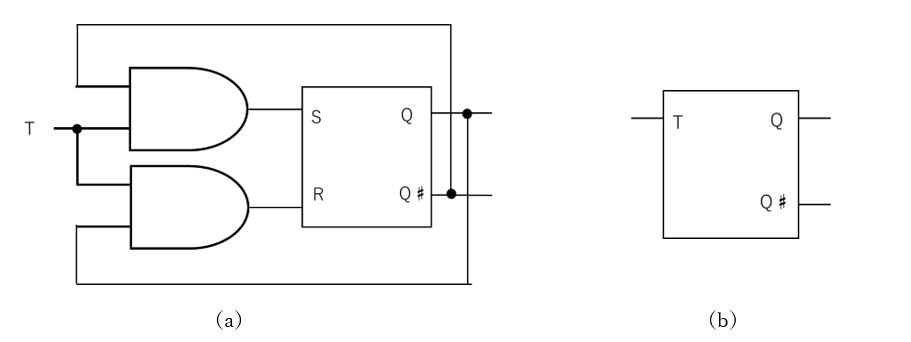

図3に、JKフリップフロップの論理回路図(a)と図記号(b)を示します。論理回路図は、RSフリップフロップに回路を追加して示しています。

また、JKフリップフロップの真理値表は図4のようになります。

【図3 JKフリップフロップの論理回路図と図記号】

【図4 JKフリップフロップの真理値表】

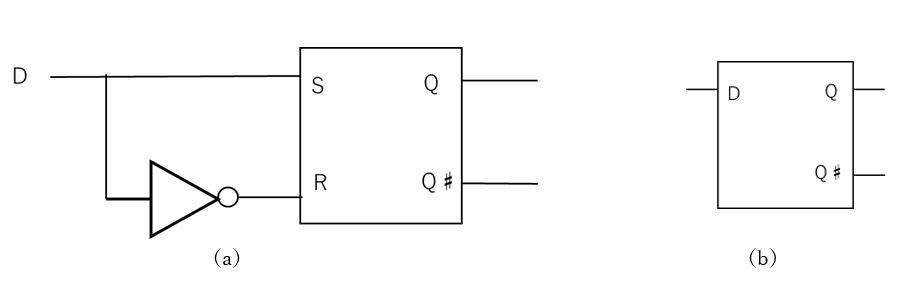

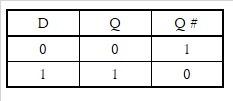

(3)Dフリップフロップ

「Dフリップフロップ」は、D=1 が入力されると1を記憶して1を出力し、D=0が入力されると0を記憶して0を出力するフリップフロップです。

他のフリップフロップと異なり、Dフリップフロップは、出力を決めるときに内部に記憶している現在の状態に依存せずに、入力だけから決まるという特徴があります。

名称のDは、このフリップフロップをクロック波形に同期させて動作するように構成した時に1クロック遅れて出力されることを表す”Delay”をとって、「Dフリップフロップ」と呼ばれます。

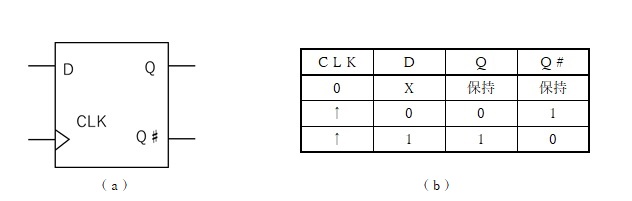

図5にDフリップフロップの論理回路図(a)と図記号(b)を示します。論理回路図は、RSフリップフロップに回路を追加して示しています。

図6ではDフリップフロップの真理値表を示します。

【図5 Dフリップフロップの論理回路図と図記号】

【図6 Dフリップフロップの真理値表】

(4)Tフリップフロップ

Tフリップフロップは、T=1 が入力されるたびにQ、Q#の0、1を反転させるフリップフロップです。

入力があるたびに出力が反転する動作が英語では”Toggle”(トグル)と表現できるので、その頭文字を取って「Tフリップフロップ」と呼ばれます。

図7にTフリップフロップの論理回路図(a)と図記号(b)を示します。論理回路図は、RSフリップフロップに回路を追加して示しています。

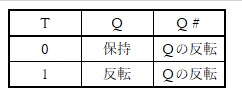

Tフリップフロップの真理値表は図8のようになります。

【図7 Tフリップフロップの論理回路図と図記号】

【図8 Tフリップフロップの真理値表】

2.同期式フリップフロップ

フリップフロップでは、複数の入力値が変化するときに、時間差があると過渡的に正しくない値が出力される可能性が出てきます。

例えば、JKフリップフロップで入力が(1、1)から(0、0) に変化する場合に2個の信号の変化に時間差があると、過渡的に(1、0)や(0、1)に対応する値が短時間出力信号線に現れる可能性があります。その値が次段の回路に入力されると回路全体の誤動作の原因になってしまいます。

したがって、誤動作などを防ぐために、信号が変化するタイミングを何らかの方法でコントロールする必要が出てきます。

そこで、信号変化のタイミングをコントロールするために一般的に行われているのが、回路全体にタイミングを決める一定周期のパルス波形を供給して、回路の各部はそのパルス波形の変化に合わせて(同期させて)動作するようにする方法です。このタイミングを決めるパルス波形を「クロック波形」や「クロック信号」と呼びます。

デジタル回路は同期式のものが多いので、フリップフロップも同期式のものが多く使われることになります。

例えば、図9はクロック(CLK)を入力するようにしたDフリップフロップの(a)図記号と(b)真理値表です。

【図9 同期式フリップフロップの例】

クロック波形と取り込みのタイミング

図9(b)において、CLKの↑は、クロック波形の立ち上がりを示し、このタイミングでDの値を取り込み、Qから出力します。

DのXはどちらの入力でもよいことを表し、CLKが0の時は、どちらの入力でもそのまま保持されます。

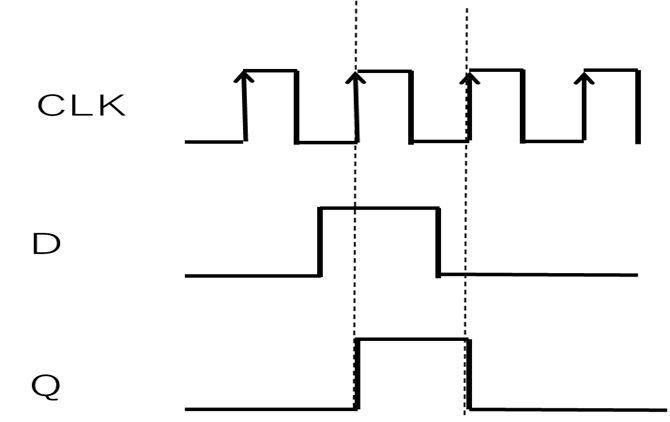

【図10 Dフリップフロップのタイミングチャートのイメージ】

図10は、図9のDフリップフロップのタイミングチャートを示しています。

クロック波形の立ち上がりでDの値を取り込んでQの出力していることが分かります。

このようにクロック波形の立ち上がりで取り込むことを「ポジティブエッジトリガ」と呼び、反対にクロック波形の立ち下りで取り込むことを「ネガティブエッジトリガ」といいます。

また同様に、RS型、JK型、T型のフリップフロップについても、クロックによって同期をとる構成を加えることができます。

以上のように、フリップフロップは、過去の入力を記憶することができる重要な回路となっており、様々な回路に応用されています。

(日本アイアール株式会社 特許調査部 E・N)

](https://engineer-education.com/wp/wp-content/uploads/2021/10/electric-circuit-dc0-150x150.png)

](https://engineer-education.com/wp/wp-content/uploads/2021/10/Circuit-element0-150x150.png)