《半導体の後工程を学ぶ③》半導体パッケージ技術の基本[リードフレーム/BGA/WLP(WLCSP) ]

![]()

今回は、一つのチップだけをパッケージに組み立てる、後工程のおさらいです。

現在生産されているIC、ディスクリートを合わせた半導体における、樹脂モールドによるパッケージ方法の割合は、最も多いのがリードフレームタイプ、次に多いのがBGAタイプ、さらにWLP(WL-CSP)タイプと続きます。

この他にも様々なタイプのパッケージがありますが、数の多い3種類について概略プロセスを説明します。

1.リードフレームタイプ

リードフレームタイプの完成品の見かけはこの図のようなものです。

![]()

前工程を終了したウェハを薄くし(バックグラインド)、チップに切り分け(ダイシング)、チップをパッケージ台座に固定し(ダイボンディング)、ワイヤでチップとリードを接続し(ワイヤボンディング)、樹脂でモールドし(モールド)、形を整えて(マーキング、リードフォーミング)、最終検査をする、というのが一連の作業です。

(1)ウェハのバックグラインド

前工程ではシリコンウェハに、ある程度の厚みがないと機械的強度が不足しますので、直径300mmのウェハで775μmの厚さが標準的です。しかし、デバイスとして搭載するには薄い方が有利ですので、50~70μm程度まで薄くします。

![]()

表面を保護テープで覆ったウェハの裏面をダイヤモンド粒子を含んだ砥石で削り、所定の厚さになったら裏面に次のダイシング工程に備えてキャリアテープを貼った後、表面の保護テープをはがします。

(2)ダイシング

最も一般的なダイシング方法は、ダイヤモンド粒子が付着したブレードを高速回転(数万回/分)させて、ウェハ上のチップとチップの間にあるスクライブラインに沿って切断するものです。ブレードの代わりにレーザを用いることもあります。

![]()

(3)ダイボンディング

キャリアテープ上に並んだチップを下からニードルで突き上げ、真空チャックでピックアップしてリードフレームのダイパッド上に運びます。

この時、前工程の最後に行ったプローブ検査で不良と判定されたチップはピックアップしないようにプログラムされています。

![]()

ダイパッドにはあらかじめ接着剤を塗布しておき、その上に移送されてきたチップをコレットでつかんでスクラブ(擦り合わせ)と加圧でダイパッドに接着します。

接着剤としては、エポキシ樹脂ベースの銀ペーストが一般的です。プロセス終了後のキャリアテープには不良チップが残ります。

![]()

(4)ワイヤボンディング

ワイヤボンディング装置は、チップ上のボンディングパッドとリード端子のチップ側をワイヤ(金線)でつなぎ、電気的に接続します。

![]()

(5)モールド

チップの固定されたリードフレームを下金型の上に置き、上金型を被せると、金型の上部と下部の間にできた隙間(キャビティー)にチップが収容されている状態になります。

![]()

この状態で金型を160~180℃に加熱してキャビティーに溶けたエポキシ樹脂を流し込み、その後金型を冷却すると、キャビティー内のエポキシ樹脂は硬化し、チップはエポキシ樹脂によって覆われることになります。

![]()

(6)マーキング、リードフォーミング

レーザやインクで、会社名やデバイスの型番、ロット番号などを記入します(マーキング)。

その後リードフレームからそれぞれのICを切り離し、リードを曲げて成型し(リードフォーミング)、実際の使用に適した形状にします。

![]()

2.BGAタイプ

![]()

BGAタイプの完成品の見かけは上のようなもので、リードフレームタイプのものでは周囲に出ていたリード端子がなく、代わりにチップ裏面に半田ボールが格子状に並んでいて(BGA: Ball Grid Array)、この半田ボールによってプリント基板と接続されます。

断面構造は下の図のようになっていて、チップは樹脂基板にダイボンディングされ、ワイヤボンディングもチップと樹脂基板上の配線の間を金線で繋いでいます。樹脂基板の表面配線と裏面半田ボールの間は樹脂基板内の配線で繋がっています。

![]()

ウェハのバックグラインド、ダイシング、までは基本的にリードフレームタイプと同様の工程ですが、ダイボンディングは樹脂基板に対して行われ、ワイヤボンディングもチップと樹脂基板上の回路との間を金線で繋ぐことになります。

![]()

モールド後、半田ボールを樹脂基板裏面に半田ボール搭載装置によって取り付けます。

マーキング後、樹脂基板から個別のデバイスを切り分けます。

・BGA基板は半導体パッケージの一種!用途や製造工程などをわかりやすく解説!

(株式会社アローテックス)

フリップチップ法による実装

BGAタイプ(およびリードフレームタイプの一部)では、樹脂基板へのチップの搭載にフリップチップ法が使われることがよくあります。これは、ICチップを上下反転(フリップ)してICチップ上の電極と基板上の電極を「バンプ」と呼ばれる金属の突起を介して直接接合するものです。

![]()

バンプは様々な方法で作ることができますが、前工程に続いてウェハ状態でパターニングしてめっきする方法が一般的です。その後、バックグラインド、ダイシング工程を経て、フリップしたチップのバンプと樹脂基板上の電極が半田などの方法で接続され、チップと基板の間に「アンダーフィル」と呼ばれる樹脂が充填されます。アンダーフィルは、チップと基板の熱膨張の差によるバンプ接続部の応力を緩和するためのものです。

フリップチップ法は、ワイヤボンディングによる接続と比べて次のような長所があります。

- チップの周りにワイヤを打つスペースを必要としないため小面積化できる

- 短距離で接続できるため、配線抵抗が小さくなる

- 1本ずつワイヤを打つのに比べ、一括接続できるためスループットが高い

3.WLP(WL-CSP)タイプ

WLP(Wafer Level Package)あるいはWLCSP(Wafer Level – Chip Size Package)は、ここまでに説明した、前工程を終了したウェハからチップを切り出してパッケージに組み立てる従来の後工程とは異なり、前工程終了後に引き続きウェハ状態のままで再配線を行い、樹脂封止、半田ボール取り付けまで行った後、チップに切り分けて製品にするという方法です。

![]()

上の図で、表面のグレーに見える部分はシリコンがむき出しで、樹脂モールドはされていません。

裏面の薄緑色で示した部分は再配線層(RDL: Re-Distribution Layer)上面の封止樹脂です。

完成品の断面を模式的に示すと下のようになります。上が裏面、下が表面です。

![]()

RDLは、シリコンチップ上の電極パッドと半田ボールの間を繋ぐ役割りを果たしており、リードフレームタイプやBGAタイプにおけるワイヤや樹脂基板上配線に代わるものです。

この構造をウェハ状態で作り終えた後、必要に応じてバックグラインドでシリコン部分の厚さ(最終的なデバイスの厚さ)を調節し、最後の工程でダイシングすることで個別のデバイスを得ます。

このようにウェハを丸ごと処理しますので、前工程歩留まりが悪いと不良チップをたくさん組み立てる(すなわち1デバイス当たりの組立コストが高くなる)ことには注意が必要です。

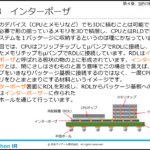

WLPと従来の後工程との比較

![]()

上の図は、WLPの後工程を、従来の後工程との対比で示しています。

前工程が、空気中のごみを極限まで減らしたいわゆるクリーンルームの中で露光装置や成膜装置、エッチング装置などの高価な設備を用いて行われるのに対して、従来の後工程は、前工程のような高度なクリーン環境を要求されず、主に機械加工的な工程からなっていました。

そこで、前工程を引き受ける、いわゆるウェハファウンドリと、後工程を専門に引き受けるOSAT(Outsourced Semiconductor Assembly and Test)が棲み分けていました。

ところがWLPタイプでは、マーキングも含めてウェハ状態のプロセスで完結し、分割(ダイシング)、テストののち出荷という手順ですので、ウェハファウンドリが後工程に進出してくる動きとOSATが高度化する動きの両方が生まれています。

さらに言えば、フォトリソグラフィ等を用いた回路形成の能力を持たない旧来のOSATのままでは、最新の後工程の流れからは取り残されてしまう可能性があるということになります。

FO-WLP

ここまで説明したリードフレームタイプ、BGAタイプ、WLPタイプはパッケージの小型化、薄型化、高機能化の歴史でもあります。しかし、チップが小型化する一方で、高機能化によって必要となる端子数が増えたにもかかわらず、端子(半田ボール)を並べられるだけの面積がないという問題が生じます。

これを解決しているのが「FO-WLP」(Fan-Out Wafer level Package)と呼ばれる技術です。

“Fan-Out”とは、再配線層をチップサイズの外にまで広げていることから呼ばれ、これに対して従来のWLPを「Fan-Inパッケージ」と呼ぶことがあります。両者を模式的に比べると下の図のようになります。

![]()

FO-WLPの基本的な構造は、再配線層がシリコンチップ上からシリコンチップを取り囲むモールド樹脂の上まで延びており、その部分(Fan-Out部)にも半田ボールが形成されています。

プロセスとしては様々な方法が提案されていますが、下に一例を示します。

![]()

最初のステップはキャリアにチップを仮固定することですが、このとき前工程の最後に行われるプローブ検査で良品と判定されたチップ(KGD: Known Good Die)だけを使うことで、FI-WLPのように不良チップまで組み立ててしまうことはありません。

キャリアとしては、直径300mmのシリコンウェハ状の物を使う場合と、大型の矩形パネル(樹脂基板、ガラス基板等)を使う場合があります。後者をFOWLPと区別して「FOPLP」(Fan-Out Panel Level Package)と呼ぶことがあります。

前者はシリコンウェハプロセス用装置を用いることができますので、精度の良い(線幅の小さい)パターニングが可能です。後者はフラットパネルディスプレープロセス用装置を用いますので、精度の点で前者に劣りますが、大面積でプロセスできますのでコスト的には有利です。

次のステップは樹脂モールドで、この後キャリアを剥離すればチップがモールド樹脂に埋め込まれた、あたかもウェハ(あるいはパネル)のような形状のものが出来上がります。

あとはFI-WLPと同様のプロセスで再配線層の形成、半田ボールの形成を行って最後にダイシングによって個別のデバイスを得ます。

上で説明したのは、①チップをキャリアに仮固定したのち樹脂で固定、②再配線層形成という順序でプロセスする、「Chip-1st」(チップファースト)と呼ばれる方法ですが、①再配線層(RDL: Re-Distribution Layer)をキャリア上に形成、②表面にバンプがあるチップを再配線層にフリップチップボンディングした後樹脂で固定するという、「RDL-1st」(RDLファースト)と呼ばれるFOWLPも開発されています。

下はRDL-1st プロセスの概略です。

![]()

ここまで一つのチップをパッケージに組み立てる工程について復習してきましたが、最後に説明したFO(Fan Out)プロセスはSiP技術に直接結びつくものです。

次回の「キーワードは”HI”|SiPの技術開発はさらに高度化・高密度化へ」では、FOプロセス以外の技術も含めて、どのようにしてSiPを実現するのかを説明します。

(アイアール技術者教育研究所 H・N)

- 第1回: 半導体開発は後工程,パッケージ技術が主役の時代へ

- 第2回: SoCとSiPを比較して解説|SiPのメリット・課題は?

- 第3回: 半導体パッケージ技術の基本[リードフレーム/BGA/WLP(WLCSP) ]

- 第4回: キーワードは”HI”|SiPの技術はさらなる高度化・高密度化へ