【パワー半導体の基礎】MOSFETの蓄積層と界面準位

前回の当連載では、バンド図を用いてMOSダイオードとMOSFETの動作原理の概要を説明しました*1)。

この記事では、その補足として、SiO2/Si界面に形成される「蓄積層」と「界面準位」の概要を紹介します。

*1) 「MOSFETの動作原理とバンド図」参照。(※併せて「pn接合の整流作用とバンド図」や「金属・半導体接合のエネルギーバンド図|ショットキー接合とオーミック接触」の記事も読んで頂くと、半導体デバイスの動作原理とバンド図の基本に関する理解が深まると思います。)

1.蓄積層

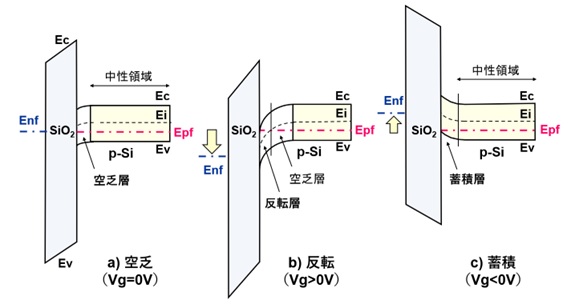

図1に、SiO2/p-Si界面のバンド図を示します。

(簡単化のため、SiO2膜中の固定電荷や界面準位は考慮していません。)

【図1 SiO2/Si界面のバンド図(p-Si:接地)】

ゲート電極とp型シリコン(p-Si)の間の電位差が変化すると、SiO2/p-Si界面近傍には「空乏」と「反転」だけでなく、「蓄積」と呼ばれる状態が形成される場合があります。

図1cに示すように、p-Siを接地した状態でゲート電極に負電圧Vgを印加すると(ゲート電極の電位がp-Siの電位よりも低くなると)、p-Si中のホールがSiO2/Si界面の方向に引き寄せられてSiO2/Si界面近傍のホール濃度が増加し、バンドが上方向に曲がります。

この時、SiO2/Si界面近傍のp-Siのフェルミ・レベルEpfと価電子帯の頂上Evの間隔(Epf-Ev)に注目すると、SiO2/p-Si界面近傍ではこの値が中性領域よりも減少しています。これは、ホール濃度が高くなっているためです。ホールが蓄積されて濃度が高くなっている領域は、「蓄積層」と呼ばれています。

「蓄積層」という用語は、SiO2/Si界面の状態を「ゲート電極とp-Siの電位差」に対応させて「形式的に分類しただけの名称」ではなく、デバイス動作中に非常に重要な役割を果たしています。

次に、その一例を示します。

2.デバイス動作時における蓄積層の働き

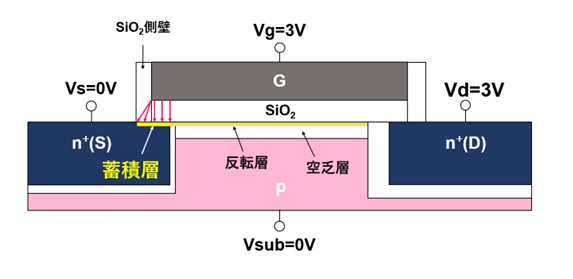

図2に、オン状態にあるNMOSの断面模式図を示します。

【図2 オン状態にあるNMOSの模式図】

ソース端のn+p接合付近に注目すると、n+/SiO2界面近傍に「蓄積層」が形成されていることがわかります。(図中の赤い矢印は、ゲート電極からソース端表面に向かう電気力線を示しています。)

この例では、接地されたソースの電位が Vg=3V のゲート電極の電位よりも低いため、n+ソース内の電子がn+/SiO2界面近傍に引き寄せられて、電子濃度が局所的に高くなっています。これが、n+ソース内に形成された電子の「蓄積層」であり、蓄積層に蓄積された電子が反転層に流入します。

実際のデバイスでは、ゲート電極形成後にSiO2膜などを用いて「側壁絶縁膜」を形成しますが、プロセス条件が不適切であると、側壁SiO2膜形成中に蓄積層の表面が酸化されてこの部分のゲートSiO2膜の厚さが増加して、蓄積層に蓄積される電子の濃度が低下し、蓄積層の寄生抵抗が増加してしまう場合があります。

ゲート長が長い場合には、ソース・ドレイン間の寄生抵抗はチャネル抵抗に支配されますが、ゲート長が短い場合には上記の問題が無視できなくなるため、注意深いプロセス設計が必要になります。

3.界面準位

完全結晶であるSi基板の表面を熱酸化すると、Si/SiO2界面ではSi結晶の周期性が失われてSiO2の非晶質構造に変化するため、Si/SiO2界面には、Si原子の配列の乱れや未反応の過剰Si原子に起因する「界面準位」というエネルギー準位が発生します。

「界面準位」は、「金属・半導体接合における整流作用」に関する実験結果を説明するために提唱された概念ですが(J.Bardeen, 1947)、SiO2/Si界面の界面準位も、界面近傍のSiの原子配列(結合状態)の乱れに起因しているという解釈(物理的モデル)は同じです。界面準位の「エネルギー位置」は、Si結晶の極めて局所的な原子配列の乱れ方などに依存すると考えられます。

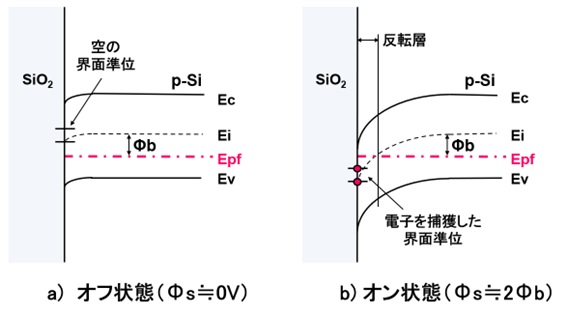

図3に、SiO2/Si界面に形成される「界面準位」の模式図を示します。

【図3 空の界面準位と電子を捕獲した界面準位】

図3aは、p-Siのバンドギャップの中央付近に二つの界面準位が形成されている場合(オフ状態)を示してます。これらの界面準位はフェルミ・レベルの上に位置しているため電子の占有率が低く、「空(から)の状態」になっています。

図3bはオン状態を示しています。表面電位Φsが上昇して強反転状態(Φs≒2Φb)になると、界面準位の位置がフェルミ・レベルよりも低くなり、反転層内電子の一部が界面準位に捕獲されています。逆に、Φsが低下して界面準位のエネルギー位置がフェルミ・レベルより高くなると、界面準位に捕獲されていた電子は放出されて、図3aのような「空の状態」に戻ります。

4.界面準位が反転層内電子に与える影響

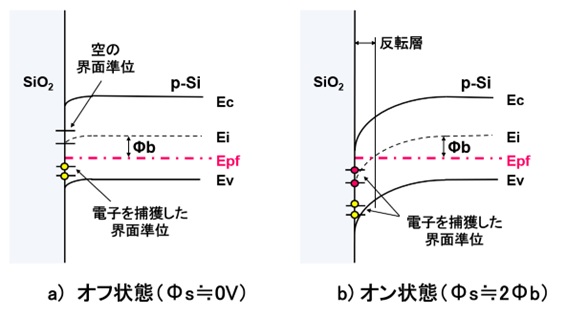

図4は、図3の例に加えて、更に二つの界面準位が形成されている場合を示しています。

【図4 界面準位が反転層内電子に与える影響】

図4の「追加された二つの界面準位」は、Epfよりもエネルギーの低い位置に形成されているため、オフ状態でも電子に占有されています。

ゲート電極に図3bと同じ値の Vg>0V を印加した場合、ゲート電極から発射された電気力線の一部は、界面準位に捕獲されている電子で終端してしまうため、図3bと同じ強反転条件を達成するために必要なVgの値(つまり閾値Vth)が高くなってしまいます。

また、強反転状態に達した場合に、反転層内電子の一部は界面準位に捕獲されるため(図4b参照)、Epf~Ec間に形成される界面準位の密度が高くなると、反転層の伝導度が低下(寄生抵抗が増加)してしまいます。

更に、界面準位に捕獲された電子は、反転層内を走行する電子との「電子・電子散乱」を引き起こすため、電子移動度の低下原因になります。

5.界面準位密度の低減方法

界面準位密度を低減するための研究は60-70年代に世界中で行われました。その結果、シリコン基板の品質向上や熱酸化条件の最適化だけでなく、「デバイス製造工程の最後に約400℃の水素雰囲気でアニールすると、未結合のSi原子が水素原子で終端され、面指数が(100)のSi基板の場合、界面準位の面密度が1012~1013cm-2から1010cm-2以下まで低減でき、MOSFETの特性が安定する」ということがわかったため*2)、現在ではこの水素処理が不可欠になっています。

*2) 面指数が(100)のSi基板表面のSi原子の面密度は約1×1015cm-2なので、単位の換算をすると、一辺の長さが0.1μmの正方形の中に1×105個の原子が周期的に並んでいることになります。従って、界面準位密度が1010cm-2の場合、Siの未結合手(dangling bond)が0.1μm(100nm)角の領域に1個存在している事になります。

6.トレンチ型MOSFETの界面準位

例えば、トレンチ型パワーMOSFET*3)では、ドライエッチング技術(RIE: reactive-ion-etching)を用いてSi基板表面にトレンチ(溝)を形成して、その側壁にゲート絶縁膜(SiO2膜)を形成するため、トレンチ側壁とSiO2膜の界面近傍の結晶構造は、面指数が(100)の完全結晶の表面とは大きく異なり、極めて複雑になります。

従って、トレンチ型MOSFETでは、トレンチの形状(深さと側壁の傾斜角度など)、エッチング条件、及びエッチング後に行う表面処理方法などに関する緻密なプロセス設計が必要になります。

また、最近注目されているSiC基板などの新材料を用いたパワーMOSFETなどの研究開発においても、界面準位の問題は最も重要な課題の一つであり、世界中で研究が活発化しています。

*3) 「パワーMOSFETの構造を解説 (IGBT/トレンチ型/スーパージャンクション型)」参照。

7.ホットキャリアー注入による界面準位密度の増加

界面準位の密度は、デバイスの動作中に(エネルギーが非常に高くなった電子の注入などによって)増加する場合があります。これは、上記のSi-H結合が高エネルギー電子の注入によって切断されて、Siの未結合手(dangling bond)が発生するためと解釈されています。

電子が高エネルギー化するメカニズムやMOSFETの特性劣化機構の詳細は割愛しますが、一例としてドレインの電界強度を定量的に把握すると、物理的イメージを描きやすくなります。

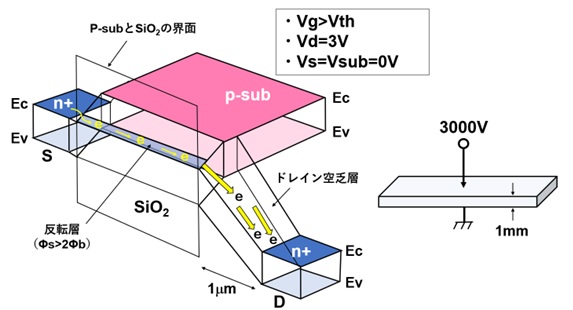

図5に、NMOS(オン状態)のバンド図を示します。

【図5 NMOS(オン状態)のバンド図】000

(図を見やすくするため、ゲート電極とゲートSiO2膜は図示していません。)

例えば、ドレイン電圧Vdが3V(Vs=Vsub=0V)で、ドレインの空乏層幅*4)が1μmになっている場合、この空乏層内の電界強度Eは、E=3V/1μm=3×106V/m=3×103V/mm となります。これは、厚さ1mmのプラスチック或いはガラスの板に、3000Vという高電圧を印加している驚異的な状態です。

Si基板の厚さ方向に電流が流れるパワーMOSFET*4)の空乏層の幅は、上記の例よりも遥かに大きくなるように設計されていますが、例えば、ドレイン電圧が300Vで空乏層幅が100μmの場合、電界強度Eは E=300V/100μm=3V/1μm となり、上記の例と同じになります。

このような高電界で加速された電子(或いは、加速された電子が衝突して発生した電子・ホール対のホール)がMOSFETのSiO2膜に注入されて、特性劣化の原因になる場合があるため、実際の半導体製品では、デバイス細部の形状や不純物分布に関する様々な改良が施されています。

*4) 「パワーMOSFETの空乏層の性質」参照。

8.おわりに

本連載「パワー半導体の基礎」では、最初に、パワー半導体が使われている最も簡単な電気回路の例を紹介し、その後で、パワー半導体の動作原理の概要を紹介しました。各記事のタイトルには「パワー半導体」という言葉がついていますが、半導体デバイスの「最も基本的な事柄」は、パワー半導体でも集積回路を構成している超微細MOSFETでも全く同じです。

微細MOSFETの分野においては、製造技術の急激な進歩に伴って、過去50年の間に、MOSFETのゲート長は約10μmから10nmまで微細化されてきました。この分野においては、ゲート長の減少に伴う「短チャネル効果」、ゲート絶縁膜の薄膜化に伴うゲート絶縁膜の信頼性問題、微細化に伴う配線抵抗の増大など様々な問題があり、MOSFETの構造は平面型から三次元構造のFINFET(フィン型FET)やGAA(gate-all-around)と呼ばれる構造に変化し、現在も急速な発展を続けています(詳細割愛)。

しかしながら、直面した諸々の問題を克服したり、新規性の高いアイデアを考案したりするために必要不可欠なのは、どの時代においても、「表面的で浅い知識」ではなく、「基本的な事柄」の「確実な理解」です。

本連載では、パワー半導体を例にして、「最も基本的な事柄」だけを並べた「飛び石」を飛ぶようなスタイルで「半導体デバイスの概要」を紹介しました。このような方法によって「基本事柄の輪郭」を初めに大まかに把握し、その後で、各自の興味や関心或いは必要性に応じて、より詳しい内容を各自のペースで(鉄道のスイッチバック方式のような方法で)じっくり掘り下げれば、理解が確実に深まるだろうと思います。

(日本アイアール株式会社 特許調査部 A・Y)