【パワー半導体の基礎】MOSFETの動作原理とバンド図

当連載の記事「パワーMOSFETの動作原理」の回では、MOSFETの動作原理を定性的に紹介しましたが、今回の記事ではエネルギーバンド図(以下、バンド図)を用いて説明します。

MOSFETは、ソースとドレインのpn接合とその間に配置されたMOS(metal-oxide-semiconductor)ダイオードで構成されており、MOSFETを流れる電流は、MOSダイオードのオン・オフによって制御されています。MOSダイオードやMOSFETのオン・オフ状態では、シリコン基板とゲート絶縁膜の界面に形成される「反転層」が重要なのですが、この状態を物理学的に理解するためにはバンド図が不可欠です。

そこで、この記事では、初めにMOSダイオードのバンド図を説明し、その後で、MOSFETのオン・オフ状態に対応するバンド図を示して、その動作原理を説明します*1)。

*1) 本連載の「pn接合の整流作用とバンド図」や「金属・半導体接合のエネルギーバンド図|ショットキー接合とオーミック接触」の各ページと併せて読んで頂くことで、半導体デバイスの動作原理とバンド図の基本に関する理解がさらに深まると思います。

1.SiとSiO2のバンド図

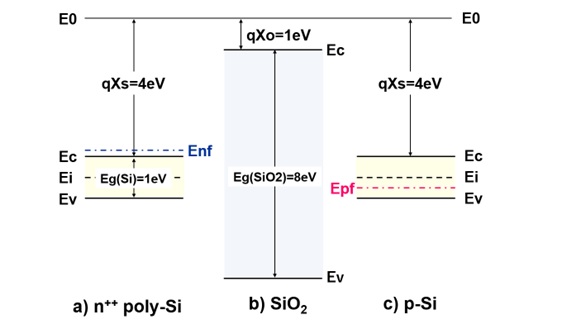

図1に、SiとSiO2のバンド図を示します。

【図1 SiとSiO2のバンド図】

E0は真空準位、Ecは伝導体(conduction band)の底、Eiは不純物を含んでいない真性Siのフェルミ・レベル(真性フェルミ・レベル)、Evは価電子帯(valence band)の頂上、Enfはn++型多結晶シリコン(poly-Si)のフェルミ・レベル、Epfはp型Siのフェルミ・レベル、Egはエネルギー・ギャップ、ΧsはSiの電子親和力、ΧoはSiO2の電子親和力です。

定量的イメージを把握しやすくするために、電子親和力の値(Χs=4.05eV、Χo=0.95eV)とEgの値(Eg(Si)=1.12eV、Eg(SiO2)≒8eV)は小数点以下を四捨五入して表示しています。

通常のバンド図では真空準位E0の線を省略しますが、前回の記事「金属・半導体接合のエネルギーバンド図|ショットキー接合とオーミック接触」でも説明したように、界面物理学の考え方を理解しながらバンド図を作成する際には、電子親和力や仕事関数の基準となる真空準位E0が不可欠です。

「E0を基準とする電子親和力の値は物質固有である」という点は、特に重要です。

2.MOS構造のバンド図

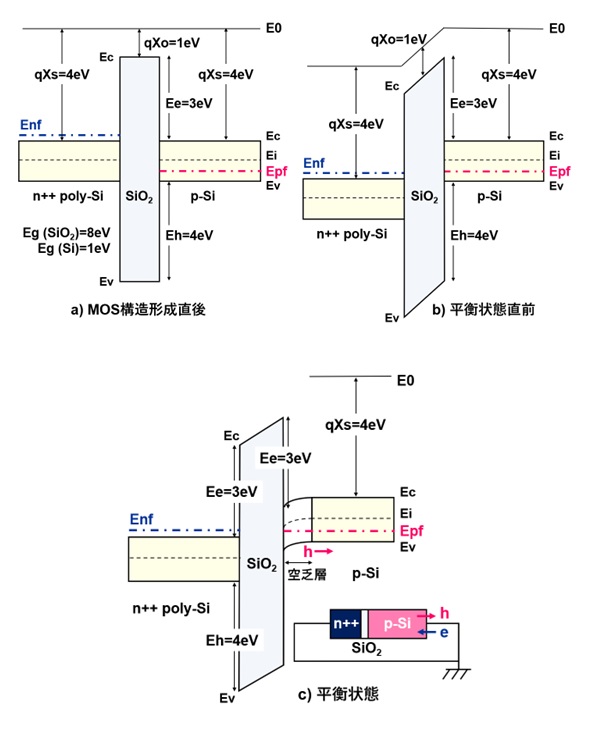

図2は、n++型poly-Si、SiO2、p-Siで構成されるMOS構造のバンド図です。

【図2 MOS構造のバンド図】

(1)MOS構造形成直後(図2a)

図2aは、MOS構造形成直後のバンド図を示しています。

電子親和力は物質固有の値であるため、n++型poly-Si/SiO2界面とSiO2/p-Si界面でも各物質の電子親和力(ΧsとΧo)の値は変わらず、真空準位E0を示す線は「連続」しています。(これは、界面物理学の重要な考え方です。)

E0を基準とするΧsとΧoの値に基づいてn++型poly-Si、SiO2、そしてp-SiのEcの線を引き、次にSiとSiO2のバンドギャップの値(Eg(Si)≒1eV、Eg(SiO2)≒8eV)に基づいてEvの線を描くと図2aのようになります。

出来上がった図を眺めると、SiのEcとSiO2のEcの間にはエネルギー障壁が存在し、その値は

Ee=qΧs-qΧo≒4eV-1eV=約3eV

であることがわかります。

また、ホールに対するエネルギー障壁の値Ehが約4eVであることも、この図からわかります。

(2)平衡状態(図2c)

図2cは、「平衡状態」のバンド図を示しています。

n++型poly-Siとp-Siの間にはSiO2膜が存在し、かつ上記のエネルギー障壁EeとEhがあるため、バンド図だけを眺めていると電荷の移動経路がわからないのですが、図2cに挿入した図に示したように、実際のMOSダイオードでは、p-Siは金属配線とのオーミック接触*2)を介して接地されているため、オーミック接触界面まで移動したホールは、配線金属中の電子と再結合して消滅します。

その結果、SiO2/p-Si界面近傍にはホールを放出して負に帯電したアクセプターが残り、n++型poly-Si/SiO2界面には電子を放出して正に帯電したドナーが残ります。n++型poly-Siの不純物濃度は非常に高いため、上方向に向かう(厚さ数nm程度の)バンドの曲がりは通常省略します。

SiO2/p-Si界面近傍のp-Siのバンドは下方向に曲がるため、「Ee≒3eV(一定)、Eh≒4eV(一定)」を考慮しながら、SiO2/p-Si界面のp-SiのEcとEvを起点にしてSiO2/p-Si界面のSiO2のEcとEvの位置を修正すると、SiO2膜のEcとEvの傾斜が図2bよりも若干緩やかになることがわかります。この変化量は、p-Siの不純物濃度に依存します。

*2)「金属・半導体接合のエネルギーバンド図|ショットキー接合とオーミック接触」参照。

(3)SiO2膜内の正電荷と界面準位の影響

熱酸化技術によってSi表面に熱酸化膜SiO2を形成すると、SiO2/Si界面近傍のSiO2膜中には(Si-O結合の状態に起因する)「正の固定電荷」が形成されます。

また、Si/SiO2界面近傍のSi表面にはSi原子の配列の乱れに起因する「界面準位」というエネルギー準位が発生し、このエネルギー準位に電子が捕獲されてしまう場合が生じます。図2は、簡単化のために、これらの二つの因子は含んでいません。

また、SiO2膜中の固定電荷や界面準位の密度は、デバイスの動作中に(エネルギーが高くなった電子の注入によってSi-O結合の状態が変化して)増減する場合もあります。

SiO2/p-Si界面近傍のp-Siのバンドの曲がり方は(p-Siの不純物濃度だけでなく)「SiO2膜中の固定電荷」や「界面準位」の密度にも依存し、MOSダイオードやMOSFETの特性ばらつきや特性不安定化の原因になりますが、この記事では、これらの詳細は割愛します。

3.MOS反転層のバンド図

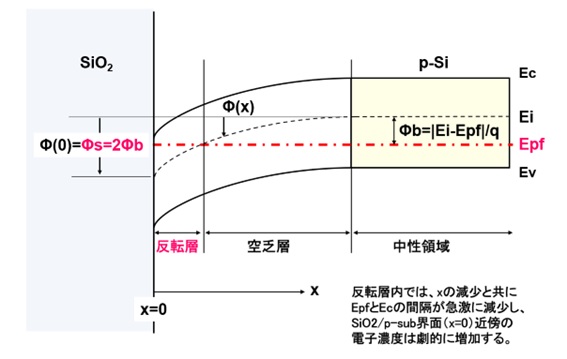

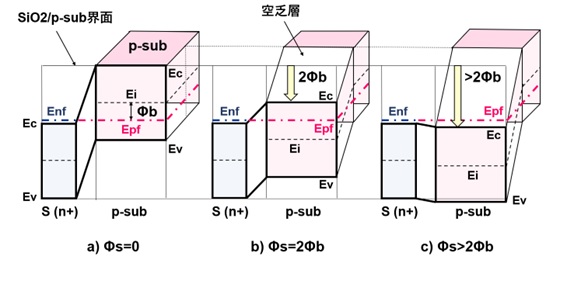

図3は、p-Siを接地して、n++型poly-Siにゲート電圧 Vg>0V を印加した時のバンド図を示しています。(n++型poly-Siは省略しています。また、SiO2膜中の固定電荷や界面準位は考慮していません。)

【図3 MOS反転層のバンド図】

p-Si内の任意の位置xにおける電位Φ(x)は「中性領域のEi」を基準としており、x=0(SiO2/p-Si界面)における電位Φ(0)は「表面電位Φs(surface potential)」と呼ばれています。(バンド図では、エネルギーは上方向が正、電位は下方向が正と定義されています。)

図3は、Vg>0V が増加して表面電位Φsが Φs=2Φb=2|Ei-Epf|/q になった状態を示しています。空乏層内のΦ(x)はVgの増加と共に増加し、空乏層内のある位置でEiの線がEpfの線と交差します。その交差した点とSiO2/p-Si界面の間を見ると、EiがEpfの下に位置しています。つまり、この領域はn型になっていることになります。

これは、Vg>0V による電界によって、空乏層内のホールは排出され、同時に、SiO2/Si界面に向かってp-Si内の電子が引き寄せられて、SiO2/p-Si界面近傍の電子濃度が増加するためです。SiO2/Si界面近傍のp-Siがp型からn型に反転しているため、この領域は「反転層」と呼ばれています。図3は、x方向に拡大して示していますが、反転層の厚さは10nm以下であり、電子濃度が非常に高い領域(SiO2/p-Si界面の極近傍)の厚さは数nm程度です。

x=0(SiO2/Si界面)における電子の濃度nは、次式で表されます*3)。

n=(ni2/Na)exp[q(Φs-Φb)/kT] ・・・(1)

ここで、niは真性Siのキャリア密度(1.45 x1010 cm-3)、Naはp-Siの不純物濃度、Φb=|Ei-Epf|/q、kはボルツマン定数(8.62×10−5 eV/K)、Tは絶対温度です。

この式から、Φsが2Φb以上になると、SiO2/Si界面に局在する電子の濃度が指数関数的に急増することがわかります。そこで、Φs=2Φb は、SiO2/p-Si界面が「強い反転状態(強反転状態)」になるための条件と呼ばれています。

*3) 式の導出過程は煩雑になるため割愛して、結論だけを示しています。詳細は、「半導体デバイス物理」に関する専門書をご参照下さい。

4.MOSFETの構造とオン・オフ状態

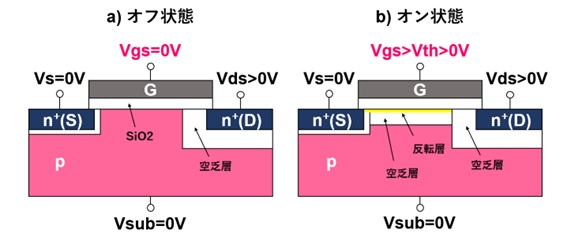

図4に、n型MOSFET(以下、NMOS)の断面構造の例を示します。

【図4 n型MOSFET(NMOS)の断面構造】

ゲート電極(G)は高濃度のリンがドープされたn++型poly-Si、ゲート絶縁膜は厚さ数10nmの熱酸化(SiO2)膜とします。

また、通常のMOSFETでは、イオン注入技術と熱処理技術を用いてソース(S)・ドレイン(D)拡散層の不純物濃度分布を制御して、ドレイン端の電界強度を緩和するための工夫が施されていますが、ここでは、シングル・ドレイン構造と呼ばれる最も単純な構造の模式図を示しています。更に、ソース・ドレイン間の距離(ゲート長)は1~10μm程度の充分大きい場合を想定しています。

次に、このNMOSのオフ状態とオン状態のバンド図を説明します。

5.NMOS(オフ状態)のバンド図

図5は、NMOSのオフ状態(Vd=3V、Vg=Vs=Vsub=0V)を示すバンド図です。図を見やすくするために、ゲート電極とSiO2膜のバンド図は示していません。また、簡単化のため、SiO2膜内固定電荷とSiO2/p-sub界面の界面準位は考慮していません。

【図5 NMOS(オフ状態)のバンド図(Sはソース、Dはドレイン。)】

ソース端のn+/p-sub接合には、Vs=Vsub=0V におけるエネルギー障壁が形成されているため、ソースからp-subへの電子の流入は生じません。

また、ドレイン端のn+p接合は Vd=3V(Vsub=0V) による逆バイアス状態になっているため、ドレインからp-subへの電子の流入は生じません。

更に、Vg=Vsub=0V であるため、SiO2/p-sub界面近傍のp-subのバンドは図2cと同じ状態にあり、反転層は形成されていません*4)。

従って、オフ状態のMOSFETでは、ソースからドレインに向かう電子の流れは完全に遮断されています。

*4) p-subの不純物濃度が低い場合や、SiO2膜内正の固定電荷の密度が高い場合には、Vg=Vs=Vsub=0V でもSiO2/p-sub界面が反転している場合があります。また、主要な事柄だけを強調するために、図5には、図2cに示したようなSiO2/p-sub界面近傍の空乏層は図示していません。

6.NMOS(オン状態)のバンド図

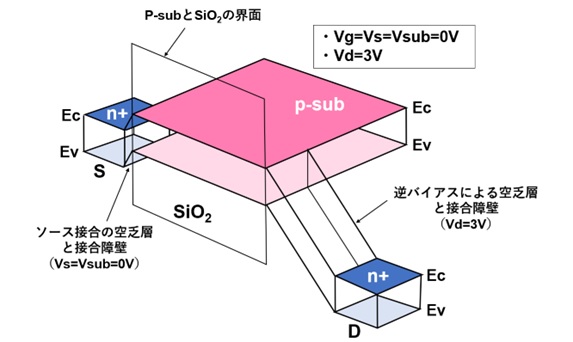

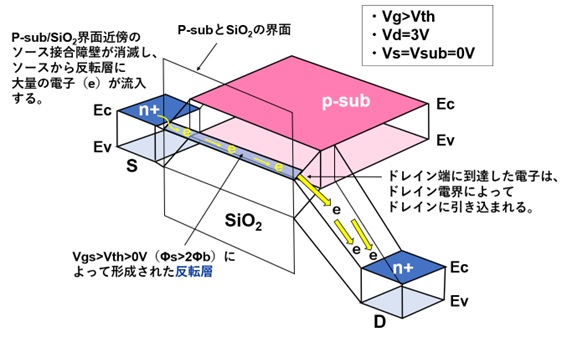

図6は、NMOSのオン状態(Vd=3V、Vg>Vth、Vs=Vsub=0V)を示すバンド図です。

Vthは、MOSFETがオン状態になるために必要なVgの最小値(閾値電圧、threshold voltage)ですが、判定に用いるドレイン電流の値などは用途によって異なるため詳細は割愛します。

ここでは、Φs=2Φb=2|Ei-Epf|/q(強反転)となるVgをVthとします。

【図6 NMOS(オン状態)のバンド図】

Vgが増加してVg≧Vth(Φs≧2Φb)になると、図3を用いて説明したように、SiO2/p-sub界面に反転層が形成されます。

この時、ソース端のn+p接合(特に、n+ソースとp-subそれぞれのEcの位置)に注目すると、SiO2/p-sub界面近傍のp-subのバンドは下方向に大きく曲がっており(Φs>2Φb)、n+p接合障壁が消滅しています。従って、ソースから反転層に大量の電子が流入します。

一方、ドレインにはVd=3Vの電圧が印加されているため、反転層(チャネル内)を走行してドレイン端に到達した電子は、ドレイン電界によってドレイン内に引き込まれます。これが、NMOSのオン状態を示すバンド図です。

この現象は「水の流れ」に良く似ているため、デバイス動作を考える多くの場面でこのアナロジー(water model)を用いることができます。

図7は、SiO2/p-sub界面近傍におけるソース接合とMOS構造のバンド図を示しています。

【図7 ソース接合とMOS構造のバンド図(Vs=Vsub=0V、Vg≧0V)】

ソース接合(n+/p-sub接合)のバンド図は、SiO2/p-sub界面における断面図を二次元表示しており、MOS構造(SiO2/p-sub)のバンド図は、斜め右側から見た三次元表示になっています。変則的な図ですが、この図によって、n+ソースのEcとp-subのEcの位置関係などを確認できます。

Φs=0V時は図7a、ソースとp-sub(Vs=Vsub=0、平衡状態:Enf=Epf)の間には高いエネルギー障壁が存在しているため、n+ソースからp-subへの電子の移動は生じません。

Φs=2Φbになると図7b、p-subのバンドがSiO2/p-sub界面に沿って下方向に移動するため、(SiO2/p-sub界面近傍の)ソース接合障壁の高さが減少します。その結果、n+ソース内のエネルギーの高い電子が反転層に流入し始めます。

Φs>2Φbになると図7c、p-subのEcの位置が更に低下してソース接合障壁が消滅します。その結果、大量の電子がソースから反転層に流入します。これは、pn接合の順方向バイアス状態*5)そのものです。

ここで、SiO2/p-sub界面におけるp-subのEpfとEcの位置関係に注目すると、EpfがEcの上に位置しています。この図からも、SiO2/p-sub界面に局在している電子の濃度が著しく高くなっていることがわかります。

*5)「【パワー半導体の基礎】pn接合の整流作用とバンド図」参照。

以上説明したように、NMOSのオン状態では、ゲート電圧 Vg>Vth>0V によって、

1)SiO2/p-sub界面に(電子濃度が非常に高い)反転層が形成され、同時に、

2)ソース接合障壁が著しく低くなる(または消滅する)ことによって、

ソースからドレインに向かう電子の経路が作られています。

次回は、「蓄積層」と「界面準位」の性質を、バンド図を用いて説明します。

(日本アイアール株式会社 特許調査部 A・Y)