【パワー半導体の基礎】パワーMOSFETの空乏層の性質

数10V~数100Vという高電圧に耐えるパワーMOSFET(metal-oxide-semiconductor field-effect transistor)では、その構成要素であるpn接合に形成される「空乏層」の制御が重要です。

この記事では、「空乏層」の性質を紹介します。

1.パワーMOSFETの構造

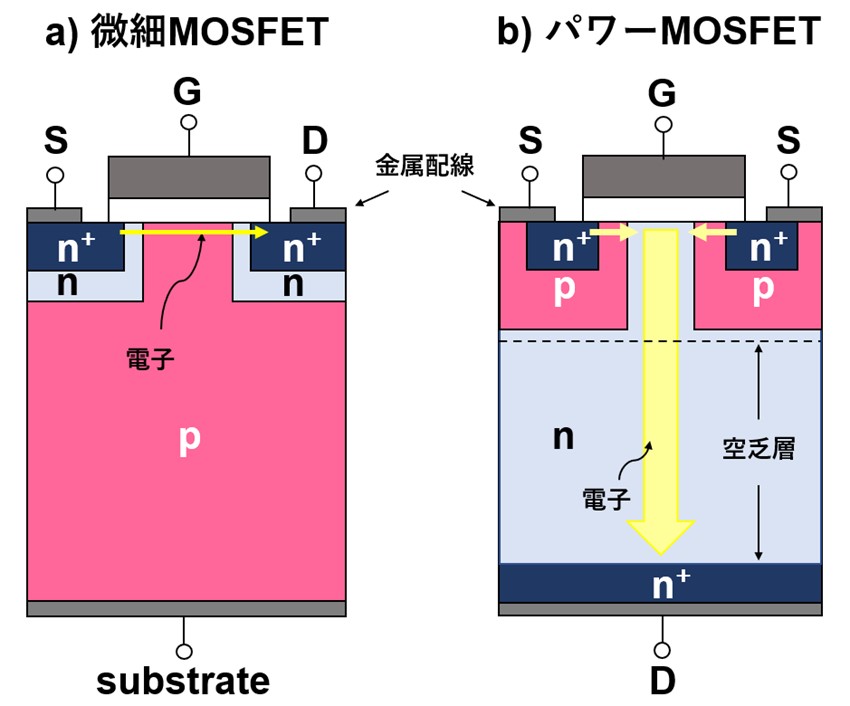

図1に、n型の微細MOSFETとパワーMOSFETの断面構造を示します。

【図1 微細MOSFETとパワーMOSFETの違い】

(図中のG、S、Dは、それぞれ、ゲート、ソース、ドレインの略。)

パワーMOSFETのドレイン側(基板の大部分)は、低濃度のn型領域になっています。

低濃度n型領域を形成する目的は、ドレインに高電圧を印加した時に形成される「ドレイン空乏層」によって「耐圧を確保する」ためですが、パワーMOSFETに要求される耐圧は非常に高いため、n型領域の厚さは数10~数100μmも必要になります。

2.空乏層幅の不純物濃度依存性

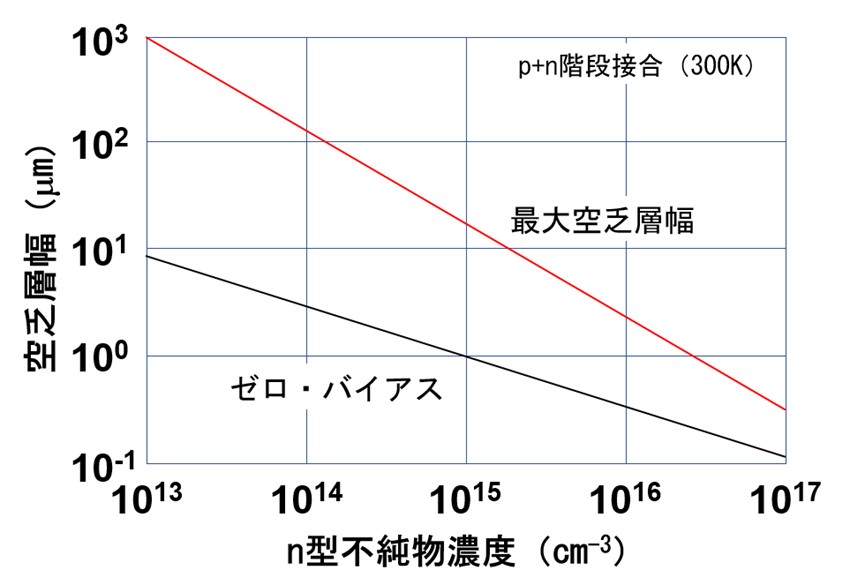

図2に、p+n階段接合*1)における「空乏層幅*2)のn型不純物濃度依存性」を示します。

ゼロ・バイアス時における空乏層の幅は、n型不純物濃度の減少と共に急増します。

例えば、n型不純物濃度が1×1017、1×1015、1×1013cm-3のとき、ゼロ・バイアス(p+n接合ダイオードに電圧をしていない状態)の空乏層幅はそれぞれ約0.1、1.0、10μmです。

【図2 空乏層幅の不純物濃度依存性】

一方、逆バイアスの値が増加すると空乏層の幅が増加し、「空乏層内の電界」で加速された電子が引き起こす「衝突電離現象」によって「絶縁破壊」に至ります。

図に示した赤い直線は、逆バイアスが絶縁破壊電圧に達するときの最大空乏層幅を示しています。

例えば、n型領域の不純物濃度が1×1015、1×1014、1×1013cm-3のとき、最大空乏層幅はそれぞれ約20、150、1000μmに達します。

*1) 「階段接合」とは、不純物濃度が接合界面で急峻に変化する接合で、複雑な要因を含む現実的なpn接合を検討する際の基本になる構造です。

*2) 空乏層はp+側とn側の両方に広がるので、空乏層の幅はp+側とn側に広がった空乏層の幅の合計になりますが、p+側(濃度>>1×1018cm-3)の空乏層幅は100~200Å程度です。

3.絶縁破壊電圧と比抵抗の不純物濃度依存性

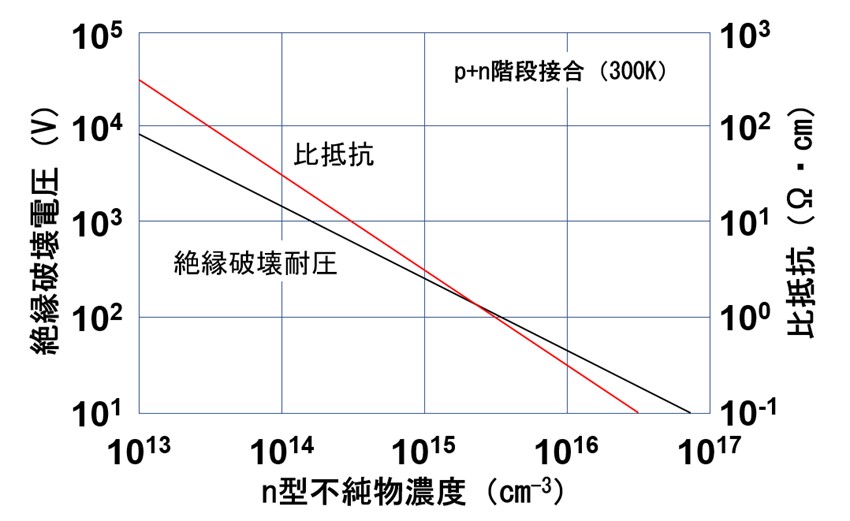

図3に「絶縁破壊電圧と比抵抗のn型不純物濃度依存性」を示します。

絶縁破壊耐圧は空乏層幅が最大値に達して絶縁破壊を起こす時の電圧で、n型不純物濃度が1×1015、1×1014、1×1013 cm-3のとき、それぞれ約250、1500、9000Vと読み取れます。従って、n型領域の不純物濃度と厚さを所望の値に調整できれば、必要な耐圧は確保できるかのように思えます。

【図3 絶縁破壊電圧と比抵抗の不純物濃度依存性】

ところが、n型不純物濃度が1×1015、1×1014、1×1013cm-3と低下すると、比抵抗はそれぞれ約3、30、300Ω・cmと急増してしまいます。つまり、n型不純物濃度を低くしてn型領域の厚さを厚くすると、当然の結果として、n型領域の寄生抵抗が急増してしまうのです。

高耐圧・高電流という厳しい特性要求を満たすためには、空乏層の基本的な性質を考慮しながら最適解を追及しなければならないため、パワーMOSFETの設計には色々な工夫が盛り込まれています。

パワーMOSFETの性能を向上するために、色々なデバイス構造が考案されてきました。

次回は、現在主流になっているパワーMOSFETの代表的な構造について解説いたします。

(日本アイアール株式会社 特許調査部 A・Y)