チップレット集積技術の最新動向と要素技術展望【提携セミナー】

半導体・電子部品実装 研究・開発 生産技術・品質保証 専門技術・ノウハウ

チップレット集積技術の最新動向と要素技術展望【提携セミナー】

おすすめのセミナー情報

もっと見る| 開催日時 | 2024/5/21(火)10:00~17:00 |

|---|---|

| 担当講師 | 栗田 洋一郎 氏 |

| 開催場所 | Zoomによるオンライン受講 |

| 定員 | 30名 |

| 受講費 | 66,000円(税込) |

★チップレット集積に向けた動向、求められる材料、パッケージ、接合、評価技術

チップレット集積技術の最新動向と要素技術展望

【提携セミナー】

主催:株式会社技術情報協会

講座内容

セミナープログラム参照

習得できる知識

チップレット集積に向けた動向、求められる材料、パッケージ、接合、評価技術について理解が深まる

担当講師

東京工業大学 科学技術創成研究院 未来産業技術研究所 特任教授 博士 (工学) 栗田 洋一郎 氏

日本アイ・ビー・エム(株) 東京基礎研究所 セミコンダクター チップレット・インターコネクト 部長 シニアリサーチサイエンティスト 青木 豊広 氏

住友ベークライト(株) 情報通信材料研究所 山下 航平 氏

愛媛大学 大学院理工学研究科 博士(工学)、 技術士(電気電子) 亀山 修一 氏

セミナープログラム(予定)

(10:00~11:30)

1.チップレット集積技術の開発動向と今後の方向性

東京工業大学 栗田 洋一郎 氏

【講演ポイント】

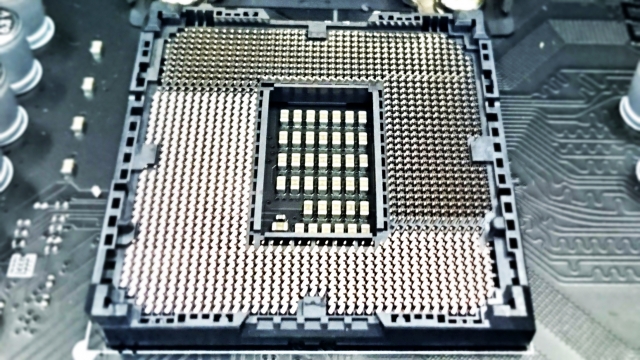

ムーアの法則の終焉に伴い、チップレット集積技術は、素子集積規模のスケールアウトやフォン・ノイマンボトルネックの解消に代表される異種集積を実現する技術として期待されており、実際のインプリメンテーションも始まっている。

このような背景や、その将来について、現在の研究状況を踏まえながら解説する。

【プログラム】

1.情報機械の歴史と半導体集積回路

2.半導体集積回路の課題

3.チップレット集積技術の現在

4.最新の研究動向

5.今後の方向性

【質疑応答】

————————–

(12:10~13:40)

2.チップレット集積を実現するパッケージ技術と接合技術

日本アイ・ビー・エム(株) 青木 豊広 氏

【講演ポイント】

チップレット集積のためのパッケージ技術として、シリコンインターポーザ、FOWLP、ブリッジ技術など様々なパッケージ技術が開発されている。AIアクセラレータを含む最先端チップレットパッケージでは、集積するチップ数の増加にともない、パッケージは巨大化、高度化している。 本講座では、チップレットの背景、求められる要求特性とチャレンジ、各パッケージ技術と接合技術の最新の開発動向を紹介する。

【プログラム】

1.チップレット

1.1 半導体デバイステクノロジーの進化とチャレンジ

1.2 チップレット

1.3 チップレット集積

2.AIアクセラレータ

2.1 AIワークロードのトレンド

2.2 学習におけるメモリバンド幅の影響

2.3 AIアクセラレータパッケージ

3.チップレット、AI向けパッケージ技術の動向

3.1 2.5D/3D

3.2 Si bridge技術

3.3 FOWLP技術

3.4 有機インターポーザ

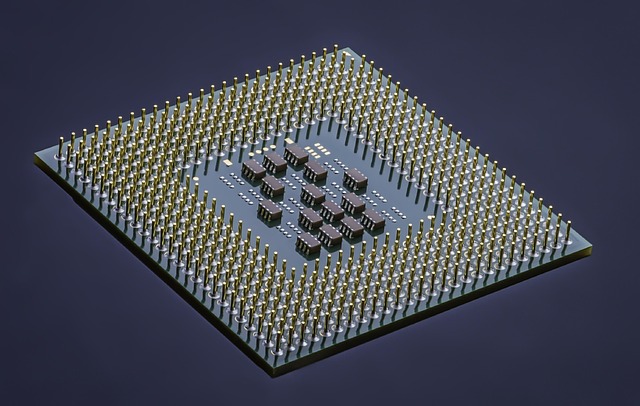

4.はんだバンプ接合技術

4.1 はんだバンプ接合プロセス

4.2 ファインピッチ接合における課題

4.3 はんだバンプ接合技術の動向

5.CoWハイブリッド接合技術

5.1 ハイブリッド接合プロセス

5.2 ハイブリッド接合の現状と課題

5.3 ハイブリッド接合の動向、技術の動向

6.まとめ

【質疑応答】

————————–

(13:50~15:20)

3.チップレットの大型・微細配線パッケージに向けた材料技術

住友ベークライト(株) 山下 航平 氏

【本講座で学べること】

半導体製造の後工程で使用される封止材料に関する基礎的な知識、および、先端半導体パッケージング向け封止材、感光材、基板材料に求められる機能、開発状況、今後の課題等についての知識が得られる。

【講座の趣旨】

本講座では、先端半導体パッケージを①WLP/PLPおよびチップレット、②SiP/AiPの2つのカテゴリーに分類し、半導体封止材を中心にそれぞれのパッケージに求められる機能や開発状況、及び今後の課題について報告する。

【プログラム】

1.半導体封止用樹脂の基礎

1.1 半導体封止材とは?

1.2 半導体封止材の構成

1.3 半導体封止材の製造プロセス

1.4 半導体封止材の使われ方

1.5 半導体封止材に使われる原材料

2.先端半導体向け材料の開発動向

2.1 WLP/PLP向け封止材の課題と対策

2.2 WLP/PLP向け感光材の課題と対策

2.3 SiP/AiP向け封止材の課題と対策

2.4 SiP/AiP向け基板材の課題と対策

【質疑応答】

————————–

(15:30~17:00)

4.チップレット実装に向けたテスト、評価技術

愛媛大学 亀山 修一 氏

【本講座で学べること】

・チップレットテストの概要

・チップレット間のインターコネクションテスト技術

・超高密度TSVの接続品質評価技術

【講座概要】

チップレットは多数のチップを1パッケージに集積する技術であり、従来のチップ単体テスト手法だけでは不十分である。パッケージ内の多数のチップ間のインターコネクション保証は重要であり、本講演ではチップレットテストのために新たに制定されたIEEE 1838規格によるインターコネクションテスト技術を紹介する。

またチップ間3D接続に必須なTSVは益々高密度化が要求されておりTSVの新たな接続品質評価技術を紹介する。

【プログラム】

1.チップレットテストの概要

1.1 チップレットとは

1.2 チップレットテストの全体工程

1.3 機能テストと構造テスト

2.チップレット間のインターコネクションテスト

2.1 チップレットは小さな実装ボード

2.2 バウンダリスキャンテストとは

2.3 IEEE 1838 規格によるチップ間インターコネクションテスト

3.TSVの接続品質評価技術

3.1 益々高密度化するTSV接続

3.2 従来の評価技術(デイジーチェーン等)の問題

3.3 アナログバウダリスキャンによるTSV精密抵抗計測方法

【質疑応答】

公開セミナーの次回開催予定

開催日

2024/5/21(火)10:00~17:00

開催場所

Zoomによるオンライン受講

受講料

1名につき66,000円(消費税込・資料付き)

〔1社2名以上同時申込の場合1名につき60,500円(税込)〕

備考

資料は事前に紙で郵送いたします。

お申し込み方法

★下のセミナー参加申込ボタンより、必要事項をご記入の上お申し込みください。

※お申込後はキャンセルできませんのでご注意ください。

※申し込み人数が開催人数に満たない場合など、状況により中止させていただくことがございます。