【半導体製造プロセス入門】集積回路(CMOS)の基本構造

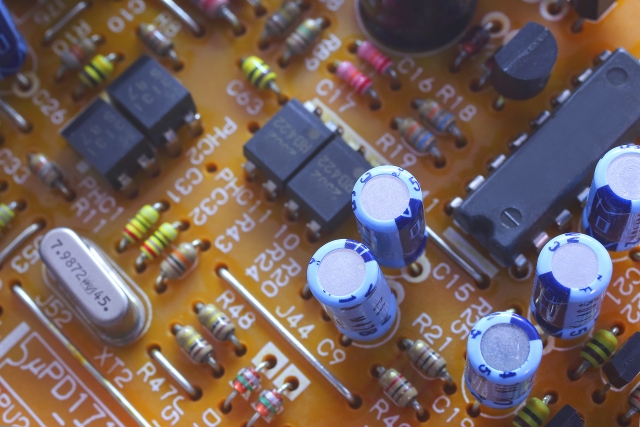

パソコンやスマホなどに使われている半導体は、そのほとんどが集積回路(IC・LSI)です。

そして、集積回路の構造を理解することは半導体製造装置を知るうえで重要です。

ここでは、一般的に使用されている集積回路の構造を説明します。

1.CMOS構造

集積回路で最も用いられるのは「MOSトランジスタ」であることは、当連載の前回「ダイオードとトランジスタから半導体デバイスの基本を学ぶ」の中で説明しました。

MOSトランジスタにはNチャネルとPチャネルの2種類があります。

実際の集積回路は、この二つのタイプのMOSトランジスタを組み合わせた「CMOS」と呼ばれる構造によって形成される場合が多いです。

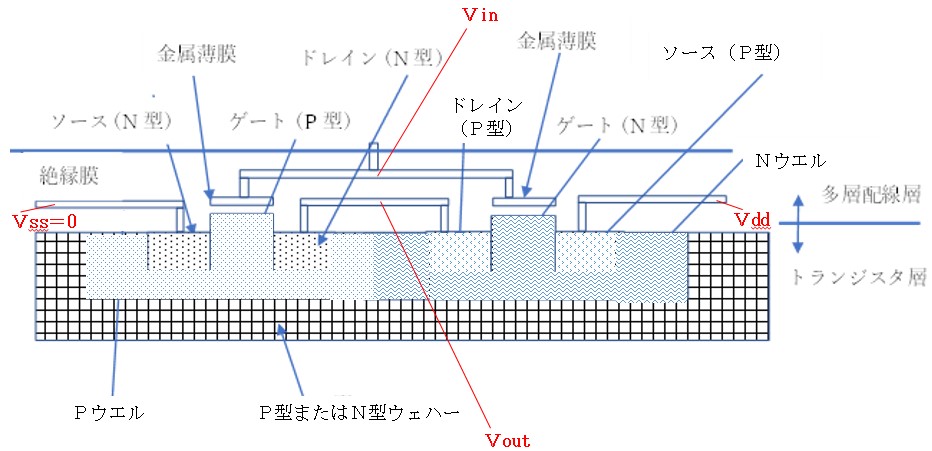

図1を見てください。

NチャネルのMOSトランジスタとPチャネルのMOSトランジスタが隣り合って並んでいます。この二種類のMOSトランジスタを電気的に接続してCMOS構造を形成します。

今、両方のゲートVinにプラスの電圧をかけるとNチャネルのMOS(NMOS)はソースとドレインが導通状態になりますが、PチャネルのMOS(PMOS)ではゲートから空乏層が広がって導通しなくなります。結果VddからVssには電流は流れず、図のVoutはVssに等しくなります。一方、Vinが0の場合、今度はPMOSが導通し、NMOSが導通しなくなって、やはりVddからVssに電流は流れず、VoutはVddに等しくなります。このようにVinの電圧が切り替わった時だけ電流が流れる仕組みになっているため消費電力をおさえることができるのです。

[図1 CMOS構造と多層配線層]

2.シリコンウェハー(ベース基板)

ここからは実際の集積回路の構造について簡単に説明します。

まず、基本となる「シリコンウェハー」について説明します。

![]()

シリコンウェハーは、不純物がほとんど存在しない実質的な純シリコンとして精製されます。そして、実際にはこの純シリコンに不純物を少しドーピングしてP型またはN型の半導体として使用します。

もちろん、どのくらいのドーピングを行うかは集積回路の目的とする最終的な特性によって変わってきます。

このあたりの塩梅は集積回路の設計者やプロセス技術者の腕の見せ所です。

3.トランジスタ層

つぎに「トランジスタ層」について説明します。

トランジスタ層はシリコンウェハーのすぐ上に形成されます。

トランジスタ層にはすでに述べたCMOS構造や抵抗、コンデンサなどの素子を形成します。

ここでもドーピング量を調整することによって、トランジスタの特性や抵抗値、コンデンサの静電容量などをコントロールすることができます。

4.多層配線層

「多層配線層」はトランジスタ層の上に形成されます。

そしてトランジスタ部に形成されたトランジスタや抵抗、コンデンサを電気的に接続し、実際の集積回路として動作させるのに必要な回路を形成します。

近年では、集積回路の集積度が飛躍的に向上しているため、トランジスタ層に形成された素子の数が多くなっており、単一層の配線だけでは間に合わなくなっています。このため、複数層の多層配線が主流となっています。

多層配線層の層間の絶縁には主に酸化シリコンが用いられ、「絶縁膜」と呼ばれます。

図1では明記していませんが、金属配線や金属薄膜の隙間が絶縁膜で埋められていると考えてください。

また、MOS型トランジスタのゲートの絶縁膜も酸化シリコンが用いられる場合が多く、多層配線層の絶縁膜を形成するときに一緒に形成される場合が多いです。

なお、実験段階ですが、絶縁の特性を上げるために空気層や、あるいは真空層を用いる可能性もあります。

次回は、半導体プロセスの「前工程」と「後工程」の概要を解説します。

(アイアール技術者教育研究所 F・S)