【パワー半導体の基礎】IGBTの動作原理|オン・オフ状態を図解で整理

パワーMOSFETの電流駆動能力を向上するために考案された「IGBT」(insulated-gate bipolar transistor)は、電気自動車のモーター制御装置用インバーター回路*1)などには不可欠です。

この記事では、IGBTの基本的な動作原理を紹介します。

*1) インバーター回路やパワーMOSFETの概要については、以下の記事をご参照下さい。

1.IGBTの基本構造

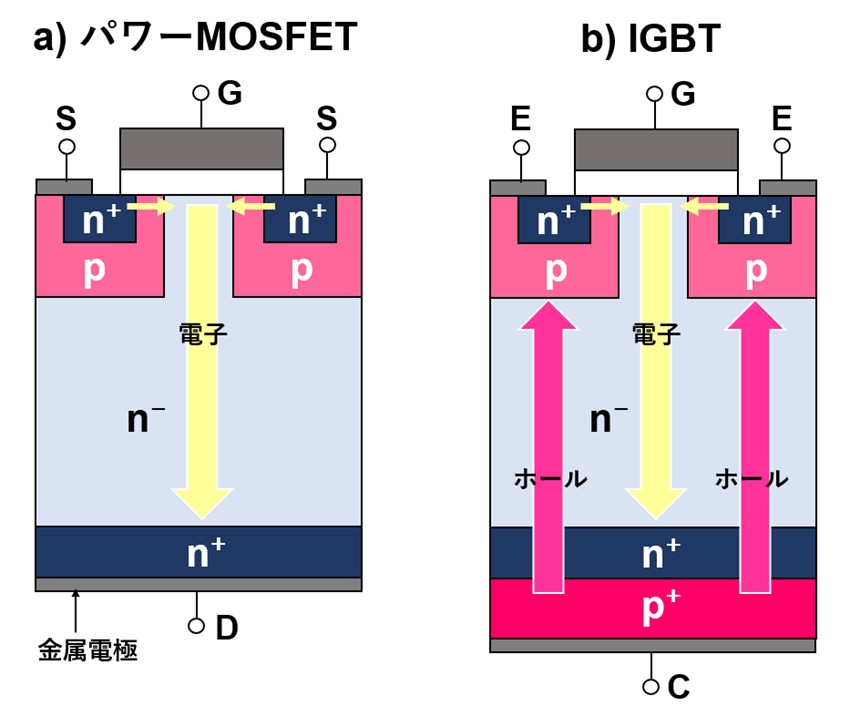

図1に、パワーMOSFETとIGBTの断面構造を示します。

【図1 パワーMOSFETとIGBTの断面構造】

(G、S、D、E、Cは、ゲート、ソース、ドレイン、エミッター、コレクターの略。)

パワーMOSFETを高耐圧化するためには、低濃度n型領域内で空乏層が充分広がれるようにしなければなりません。そのためには、n型領域の不純物濃度を低くし、厚さを充分厚くしなければなりません。その結果、オン状態におけるn型領域の抵抗が高くなり、導通損失(オン状態のときに発生する熱損失)が大きくなってしまいます。この導通損失を低減するために考案されたのがIGBTです。

図1に示した断面構造(模式図)では、IGBTは、パワーMOSFETの基板底部にp+層を追加しただけのように見えますが、このp+層が追加されたことによって、IGBTは、パワーMOSFETの底部にp+n+接合ダイオードを直列接続した構造になっています。これは、デバイス物理の深い理解に基づく「画期的な発明」(山上、赤桐:特公昭47-21739(1971)、1968年世界初の出願)でした。

初期のパワーMOSFETとIGBTでは、それぞれ高濃度n+型Si基板と高濃度p+型Si基板の上に不純物濃度の低いn型Si層をエピタキシャル成長し、そこにMOSFETのゲート、p型領域、及びソースなどが形成されていました。図1に示した模式図では、パワーMOSFET底部のn+層とIGBT底部のp+層は薄い層のように見えますが、実際は、それぞれn+型Si基板とp+型Si基板です。

2.IGBTのオン・オフ状態

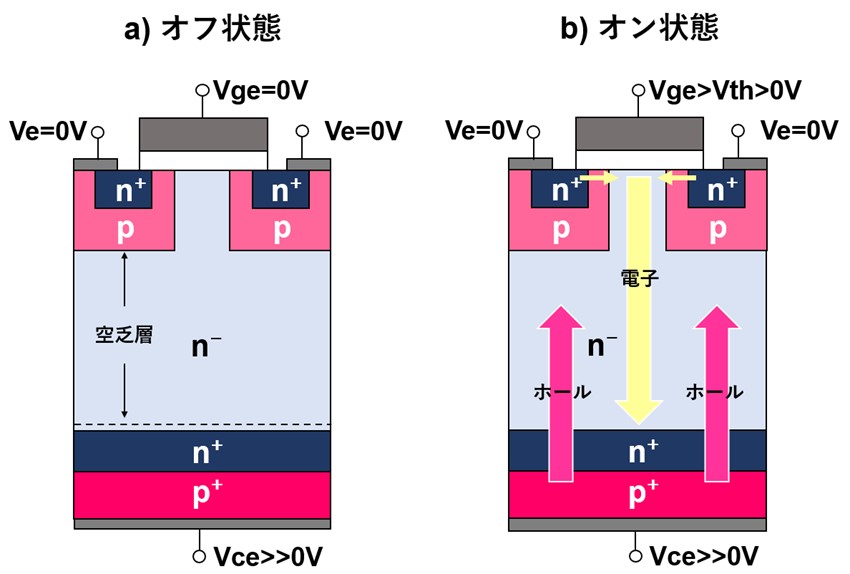

次に、IGBTのオン・オフ状態の概要を説明します(図2参照)。

【図2 IGBTのオフ状態とオン状態を示す模式図】

オフ状態 (図2a参照)

基板表面のn+(emitter)を接地した状態で、Si基板底部のp+(collector)に例えば600Vという高い電圧(Vce)を印加すると、基板表面のp型領域と低濃度n型領域から成るpn接合が逆バイアス状態になり、低濃度n型領域に大きな空乏層が形成されます*2)。ゲート電圧(Vge)が閾値電圧(Vth)よりも低い状態ではゲートが閉じた状態であるため、電子もホールも流れません。

*2) 基板表面側のp型領域にも空乏層が広がりますが、p型不純物の濃度が高いので空乏層幅は非常に小さいため、(図2)では省略しています。 空乏層幅の不純物濃度依存性については、パワーMOSFETの空乏層のページをご参照ください。

オン状態 (図2b参照)

ゲート電圧(Vge)が閾値電圧(Vth)よりも高くなると、チャネル領域に反転層が形成され、基板表面のn+(emitter)から基板内部の低濃度n型領域に向かって大量の電子が流入し、基板表面から基板底面に向かう電子流が発生します。これは、パワーMOSFETのソースからドレインに向かう電子流に相当します。

このとき、IGBTでは、基板底部のp+n+接合ダイオードが順バイアス状態になり、p+n+接合から低濃度n型領域に向かって大量のホールが流れ込みます。その結果、低濃度n型領域内の電子とホールの濃度が劇的に増加してオン抵抗が低くなるため、電流駆動能力が著しく向上します。

オフ状態へのスイッチング

ゲート電圧(Vge)が閾値電圧(Vth)よりも低くなると反転層が消滅して、低濃度n型領域への電子の流入が止まり、ホールの流入も止まります。この時、低濃度n型領域には「オン状態の間に大量に流れ込んでいた電子とホール」が存在しており、これらが「再結合」によって消滅するまでの間は「テール電流」と呼ばれる電流が流れ続け、「ターン・オフ損失」の増加要因になります。

IGBTではこの現象を避けることが容易でないため、使用可能なスイッチング周波数に限界があり、その限界値よりも高速のスイッチング性能が必要な分野ではパワーMOSFETに頼るしかありません。

テール電流を減らすためには、ホールの注入効率を低減する方法が有効であり、そのためには基板底部のp+の不純物濃度を低減する必要があります。

IGBTでは、大量のホール注入による「導通損失の低減」とテール電流による「ターン・オフ損失の増加」は、常にトレード・オフの関係にあります。

IGBTに固有の問題を克服するために考案された新しい構造については、次回「IGBTの主なデバイス構造を解説|PT型/NPT型/FS型」で紹介します。

(日本アイアール株式会社 特許調査部 A・Y)