Co-Packaged Opticsの最新動向と 実装、光結合技術【提携セミナー】

通信技術 半導体・電子部品実装 研究・開発 専門技術・ノウハウ

Co-Packaged Opticsの最新動向と 実装、光結合技術【提携セミナー】

おすすめのセミナー情報

| 開催日時 | 2024/06/14(金)10:30~16:15 |

|---|---|

| 担当講師 | 高武 直弘 氏 |

| 開催場所 | Zoomによるオンライン受講 |

| 定員 | 30名 |

| 受講費 | 60,500円(税込) |

★高効率な光結合技術、光トランシーバ、シリコンフォトニクスの最新動向

Co-Packaged Opticsの最新動向と

実装、光結合技術

【提携セミナー】

主催:株式会社技術情報協会

講座内容

1.超小型光トランシーバの開発動向とCo-Packaged実装技術

2.光電コパッケージ用シリコンフォトニクス内蔵パッケージ基板の開発

3.UV硬化樹脂を用いたシリフォトチップとファイバ間接続デバイス技術

習得できる知識

【第1部】

- データセンタ内の高速データ伝送と光トランシーバの変遷

- Co-Packaged Opticsと高密度電気・光実装に対する技術課題

- Mosquito法を用いたポリマー光導波路

【第2部】

- 光電コパッケージ技術の概要と動向

- 光実装技術の課題

- シリコンフォトニクス内蔵パッケージ基板を用いた光電コパッケージ技術

【第3部】

1) シリコンフォトニクスチップ(SiPh)とは?

2) SiPhと単一モードファイバ(SMF)間の光結合の問題点とその解決策は?

3) キー材料&技術であるUV硬化樹脂・自己形成光導波路(SWW)技術・マスク転写技術とは?

4) SMF側への取り組み:光スポットサイズを小さくする方法は?

5) SiPh側への取り組み:光スポットサイズを大きくする方法は?

6) アレイ化への取り組みは?

担当講師

【第1部】(株)日立製作所 研究開発グループ エッジコンピューティング研究部 研究員 博士(工学)

高武 直弘 氏

【第2部】(国研)産業技術総合研究所 プラットフォームフォトニクス研究センター 主任研究員 博士(工学)

乗木 暁博 氏

【第3部】マレーシア工科大学 客員教授 工学博士 三上 修 氏

セミナープログラム(予定)

<10:30~12:00>

1.超小型光トランシーバの開発動向とCo-Packaged実装技術

(株)日立製作所 高武 直弘 氏

【講座概要】

データセンタのトラフィックの急増に対応するため、光トランシーバの重要性が増している。高速・大容量化に対応するには、データ伝送速度の高速化だけでなく、光トランシーバの小型化・高密度化が重要で、小型で高効率な電気・光実装技術の研究開発が進んでいる。そこで本講座では、超小型光トランシーバの概要と、低クロストーク性を有する高密度実装技術について説明する。さらに、光トランシーバの新たな適用形態であるCo-Packaged Opticsで有望なGI型円形ポリマー光導波路を用いた小型・高効率な光結合技術を紹介し、光結合効率と光リンク特性について述べる。

1.研究背景

1.1 データセンタ内の高速データ伝送と光インターコネクトの必要性

1.2 光インターコネクト向け光トランシーバの適用形態の変化

1.3 Co-Packaged Opticsと高密度電気・光実装に対する要求・技術課題

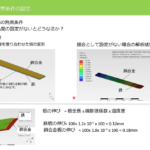

2.狭幅絶縁層を有するグランド電極構造による高密度・低クロストーク実装技術

2.1 高密度実装時のクロストーク発生要因と狭幅絶縁層を有するグランド電極構造

2.2 等価回路モデルとクロストーク解析

2.3 提案構造の放熱特性への影響

2.4 光トランシーバの試作と光リンク特性評価

3.90°曲げGI型ポリマー導波路を用いた小型・高効率光結合技術

3.1 ポリマー導波路を用いた光結合の重要性とMosquito法

3.2 90°曲げGI型導波路の構造最適化

3.3 ポリマー導波路の試作と挿入損失測定

3.4 光リンク特性評価

4.まとめ

【質疑応答】

<13:00~14:30>

2.光電コパッケージ用シリコンフォトニクス内蔵パッケージ基板の開発

(国研)産業技術総合研究所 乗木 暁博 氏

【講座概要】

データセンターや大規模科学計算、AIシステムにおいて、より大容量、低遅延、低電力な信号伝送技術が求められている。光電コパッケージ技術は、超小型の光トランシーバを半導体パッケージ内部に集積しボトルネックとなっていた電気配線を除去する技術であり、信号伝送の劇的な性能向上につながると期待されている。本講座ではそのような光電コパッケージ技術のロードマップや世界的な動向について解説するとともに、弊所で進める次世代の光電コパッケージ技術を紹介する。

1.光電コパッケージ技術の概要

1.1 背景

1.2 光電コパッケージのロードマップ

1.3 世界的な光電コパッケージの取り組み例

2.シリコンフォトニクス内蔵パッケージ基板の開発

2.1 シリコンフォトニクス内蔵パッケージ基板の概要

2.2 要素技術

2.2.1 マイクロミラー

2.2.2 シングルモードポリマー導波路

2.2.3 光IC埋め込み技術

2.2.4 光コネクタ

2.2.5 熱解析

2.3 試作と信号伝送評価結果

2.4 今後の課題

3.まとめ

【質疑応答】

<14:45~16:15>

3.UV硬化樹脂を用いたシリフォトチップとファイバ間接続デバイス技術

マレーシア工科大学 三上 修 氏

【講座概要】

将来の高速大容量光ネットワークを実現するキーデバイスの一つとして、シリコンフォトニクスチップ(SiPh)が注目されている。SiPh 内の光配線はごく微小な断面積を有していることが特徴であり、ネットワークに使用されている単一モード光ファイバ(SMF)の光スポットサイズとは大差があり、結合効率が低いことが問題である。SiPhチップとSMF両者を高効率に接続するためには、両端面での光スポットサイズを一致させることが不可欠である。

本講演では、この目的のための内外の研究機関での取り組みを紹介するとともに、東海大学で進めているUV硬化樹脂と自己形成光導波路(Self-Written Waveguide:SWW)技術を用いたアプローチを紹介する。本アプローチは特別に高価なプロセス装置を必要とせずに、簡易なプロセスで高い結合効率の実現に対応できる可能性がある。この分野の研究開発に従事されている諸氏の一助になることを願っている。

1.シリフォトチップとは

2.シリフォトチップとファイバ接続の取り組み

2.1 表面結合

2.2 端面結合

3.結合デバイス製作技術と材料

3.1 UV硬化樹脂

3.2 自己形成導波路技術

3.3 マスク転写技術

4.Spot Size Down Converter:ファイバ側への取り組み

4.1 テーパピラー構造

4.2 ピラー・マイクロレンズ構造

5.Spot Size Expander:シリフォトチップ側への取り組み

5.1 ピラー・マイクロレンズ構造

6.結び

【質疑応答】

公開セミナーの次回開催予定

開催日

2024/06/14(金)10:30~16:15

開催場所

Zoomによるオンライン受講

受講料

1名につき60,500円(消費税込み,資料付)

〔1社2名以上同時申込の場合のみ1名につき55,000円〕

備考

資料は事前に紙で郵送いたします。

お申し込み方法

★下のセミナー参加申込ボタンより、必要事項をご記入の上お申し込みください。

※お申込後はキャンセルできませんのでご注意ください。

※申し込み人数が開催人数に満たない場合など、状況により中止させていただくことがございます。