先端半導体パッケージングの技術トレンド IEDMやECTCで発表されたハイブリッド接合やチップレットインテグレーション技術を中心に、3D-IC/TSVからFOWLPまで【提携セミナー】

半導体・電子部品実装 半導体/電子 研究・開発 生産技術・品質保証 専門技術・ノウハウ

先端半導体パッケージングの技術トレンド IEDMやECTCで発表されたハイブリッド接合やチップレットインテグレーション技術を中心に、3D-IC/TSVからFOWLPまで【提携セミナー】

おすすめのセミナー情報

もっと見る| 開催日時 | 2023/7/27(木) 10:30-16:30 |

|---|---|

| 担当講師 | 福島 誉史 氏 |

| 開催場所 | Zoomによるオンラインセミナー |

| 定員 | - |

| 受講費 | 【オンラインセミナー(見逃し視聴なし)】:47,300円 【オンラインセミナー(見逃し視聴あり)】:52,800円 |

先端半導体パッケージング技術の最新動向を解説!

6月の国際会議(ECTC)の情報もご紹介する予定です。

先端半導体パッケージングの技術トレンド

IEDMやECTCで発表されたハイブリッド接合や

チップレットインテグレーション技術を中心に、

3D-IC/TSVからFOWLPまで

《材料を含めた個別プロセスを詳細に解説》

【提携セミナー】

主催:株式会社情報機構

世界中の先端ロジック半導体の生産を一手に担う台湾TSMCが200億円弱を投じて3D-ICの研究開発拠点を日本に建設するとの話がでてから一年以上経過した。ムーアの法則の次なるテクノロジードライバーは何か?数々の有望なデバイスの研究開発が進められている中で、今後も半導体産業ではSiが主役であり、その後は集積回路を積み重ねて三次元構造にした3D-ICが性能のスケーリングを牽引するとの見方が多い。

本講座では、3D-ICを中心とした先端の半導体パッケージング技術に焦点を当て、最近の研究開発動向を詳解する。また、世界最大の半導体パッケージング技術の国際会議であるECTCで2023年6月に発表される最新の内容についても紹介する。さらに、先端半導体パッケージング技術を駆使してフレキシブルエレクトロニクスの高性能化を志向したフレキシブル・ハイブリッド・エレクトロニクス(FHE)についても解説する。

◆ 受講対象者

材料メーカー、半導体製造装置メーカー、

次世代デバイスの設計・研究開発・生産製造に携わる方(初心者から中級者まで)。

新たに半導体パッケージングや3D-ICの研究開発に取り組むことになった方々や

新人への研修などを目的としてもかまいません。

◆ 本セミナーに参加して修得できること

- 先端半導体パッケージを俯瞰した基礎知識

- 3D-IC/TSV技術の詳細

- 3D-ICとFOWLPの比較、課題の理解、今後取り組むべき研究開発の方向性

- FHE(フレキシブル・ハイブリッド・エレクトロニクス)によるフレキシブルデバイスの高性能化

担当講師

東北大学 大学院工学研究科 機械機能創成専攻 准教授 博士(工学) 福島 誉史 氏

セミナープログラム(予定)

1.先端半導体パッケージの技術動向:ムーアの法則の次なる牽引薬は?

2.FOWLP

2.1 FOWLPの概要と歴史

2.2 FOWLPの分類(Die-first, RDL-first, InFO)と特徴

2.3 FOWLPの課題

2.4 FOWLP の研究開発動向

3.3D-IC

3.1 3D-ICの概要と歴史

3.2 3D-ICの分類

3.2.1 積層対象による分類(Wafer-on-Wafer vs. Chip-on-Wafer)

3.2.2 積層形態による分類(Face-to-Face & Back-to-Face)

3.2.3 TSV形成工程による分類(Via-Middle vs. Via-Last)

3.2.4 接合方式による分類等

3.3 TSV形成技術

3.3.1 高異方性ドライエッチング(Bosch etch vs. Non-Bosch etch)

3.3.2 TSVライナー絶縁膜堆積

3.3.3 バリア/シード層形成

3.3.4 ボトムアップ電解めっき

3.4 チップ/ウエハ薄化技術

3.5 テンポラリー接着技術

3.6 アセンブリ・接合技術

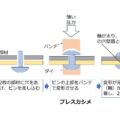

3.6.1 微小はんだバンプ接合技術とアンダーフィル

3.6.2 SiO2-SiO2直接接合

3.6.3 Cu-Cuハイブリッドボンディング

3.6.4 液体の表面張力を用いた自己組織化チップ実装技術

4.各社の先端半導体パッケージング技術の開発動向

4.1 ソニー社イメージセンサ技術

4.2 新光電気社の2.3Dインターポーザ技術”i-THOP”

4.3 三次元DRAM技術”HBM”

4.4 TSMC社のFOWLP技術”InFO”

4.5 TSMC社のChip-on-Wafer積層技術”CoWoS”

4.6 Intel社のSi Bridge技術”EMIB”

4.7 Intel社の3D-IC/TSV技術”Foveros”(再定義されたFoveros OmniとFoveros Direct)

5.チップレットインテグレーションの最前線

-AMD社の3D V-Cacheの例を挙げて徹底解説

6.多様化する半導体パッケージング

7.―国際会議ECTCにおける今年と来年の動向―

8.おわりに

公開セミナーの次回開催予定

開催日

2023年7月27日(木) 10:30-16:30

開催場所

Zoomによるオンラインセミナー

オンライン配信のご案内

★ Zoomによるオンライン配信

★ 見逃し視聴

については、こちらをご参照ください

受講料

【オンラインセミナー(見逃し視聴なし)】:1名47,300円(税込(消費税10%)、資料付)

*1社2名以上同時申込の場合、1名につき36,300円

【オンラインセミナー(見逃し視聴あり)】:1名52,800円(税込(消費税10%)、資料付)

*1社2名以上同時申込の場合、1名につき41,800円

*学校法人割引;学生、教員のご参加は受講料50%割引。

●録音・録画行為は固くお断り致します。

備考

※配布資料・講師への質問等について

●配布資料はPDF等のデータで送付予定です。受取方法はメールでご案内致します。

(開催1週前~前日までには送付致します)。

*準備の都合上、開催1営業日前の12:00までにお申し込みをお願い致します。

(土、日、祝日は営業日としてカウント致しません。)

●当日、可能な範囲で質疑応答も対応致します。

(全ての質問にお答えできない可能性もございますので、予めご容赦ください。)

●本講座で使用する資料や配信動画は著作物であり

無断での録音・録画・複写・転載・配布・上映・販売等を禁止致します。

お申し込み方法

★下のセミナー参加申込ボタンより、必要事項をご記入の上お申し込みください。

★【オンラインセミナー(見逃し視聴なし)】、【オンラインセミナー(見逃し視聴あり)】のいずれかから、ご希望される受講形態をメッセージ欄に明記してください。