《MOSFET/CMOS/JFET他》電界効果トランジスタの構造と仕組みがわかる!

半導体デバイスの解説として、前回の連載ではバイポーラトランジスタの原理と構造をご説明しました。

今回は、トランジスタのもう一つの分類である「電界効果トランジスタ(FET)」について解説します。

1.電界効果トランジスタとは?

「電界効果」は”Field Effect“の日本語訳です。

「電界効果トランジスタ」(Field Effect Transistor)とは、半導体内部の電界によって電流を制御するタイプのトランジスタで、もっぱら「FET」と略称されます。

[※関連記事:3分でわかる FET(電界効果トランジスタ)とは?原理・特徴・用途の要点解説 ]

2.MOSFETとは?

FETの代表が「MOSFET」(Metal Oxide Semiconductor FET)で、電界効果をどのような構造で生み出しているかをFETの前につけてデバイス名にしています。この場合、金属、酸化物、半導体の接合を使っていることを示しています。

MOSFETは、「MISFET」(Metal Insulator Semiconductor FET)の一種ですが、シリコンの場合、シリコン酸化膜(Oxide)が非常に良い絶縁体(Insulator)なので集積回路等に多用され、電界効果トランジスタと言えばMOSFETのこと、と言うぐらいに電界効果トランジスタの代表的存在になっています。

MOSFETの構造と仕組み(原理)

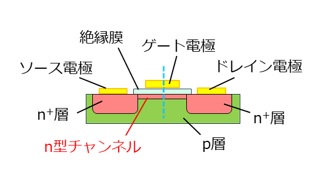

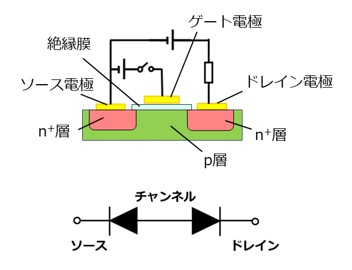

図1は、MOSFETの動作時の断面模式図です。

ソース電極からドレイン電極に向かって、n型チャンネルを流れる電子を、ゲート電極に印加する電圧によって制御します。n型チャンネルは常に存在するのではなく、絶縁膜との境界部分のp層を、ゲート電圧によってn型に変えることで作られます。

【図1 MOSFETの断面構造】

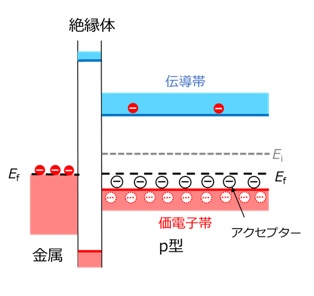

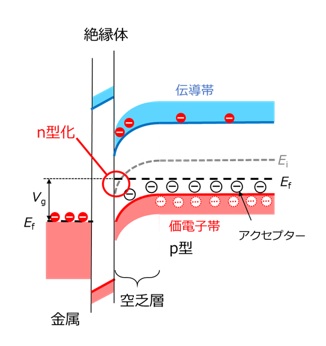

図1の青点線にそって、バンド図を見てみましょう。

【図2 MOSFETのゲート電極部のバンド構造】

図2のように、ゲート電極金属とp型半導体が、絶縁体膜をはさんで向き合っています。簡単のために、ゲート電極と半導体の間に電圧をかけない状態でp型のバンドに曲がりはない(絶縁体との界面に空乏層がない)とします。

図中のEiは、半導体が真性半導体であるときのフェルミ準位の位置、すなわち、フェルミ準位がこの位置の時、伝導帯の電子数と価電子帯の正孔数が一致するようなエネルギー位置を示しています。

この状態(すなわちゲートに電圧がかかっていない状態)では、図3に示すようにソースのn+層とドレインのn+層の間はp層なので、ソース、ドレイン間に電圧をかけても電流は流れません。

ソース、ドレイン間はn-p-nの接続で、二つのダイオードが逆方向に接続された形になっているのです。

【図3 ゲートに電圧がかかっていない状態のMOSFET断面図(上)と、

その状態をダイオードで表した概念図(下)】

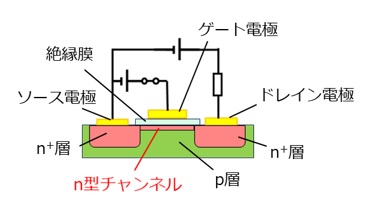

この状態から金属側に正のバイアス(Vgs)をかけていくと、図4のようにバンドが曲がって半導体界面に空乏層が広がっていき、界面の近傍ではEfがEiより高くなる、つまり伝導帯の電子数のほうが価電子帯の正孔数より多くなります。これは界面付近がp型からn型に変わることを意味します。これを「反転層」と言い、こうしてn型チャンネルが作られ、ソース、ドレイン間はn-n-nと結ばれて電流が流れることができます(図5)。

反転層ができ、電流が流れ始める時のVgsをしきい値電圧(Vth)と言います。

電流量は、ゲート電圧が高いほど大きくなります。

【図4 MOSFETのゲート電極に電圧を印加した時のバンド構造】

【図5 ゲートに電圧がかかり、反転層ができた状態のMOSFET断面図】

次にソース、ドレイン間に電圧をかけた場合にどうなるかを見ていきます。

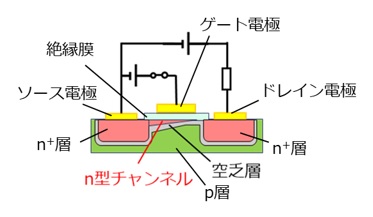

ゲート電圧を一定にしたままドレイン電圧(Vds)を上げていくと、半導体側はソースからドレインに向かって電位が上がっていくのに対して、金属のゲート電極ではどの場所でも電位が変わらないため、 Vds>Vgs–Vthの場合、ゲート電極のドレイン寄りで、チャンネルがなくなって空乏層ができるということになります。

これまでに示した図では省略していた空乏層を含めて描くと図6のようになり、n型チャンネルを流れてきた電子は、空乏層中をドレインに向かって落ちて行きます。

こうなると、Vdsをこれ以上大きくしてもドレイン電流は増えず、ほぼ一定になります。

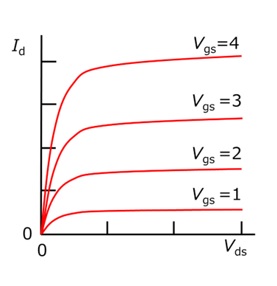

従って、ドレイン電圧Vdsとドレイン電流(Id)の関係をゲート電圧(Vgs)をパラメータに示すと図7のようになります。

【図6 ドレイン電圧を上げ、ゲート電極のドレイン寄りで

チャンネルがなくなった状態のMOSFET断面図】

【図7 Vgsをパラメータにした、Id–Vds特性】

2.CMOSとは?

上記で説明したn型チャンネルのMOSFET(NMOS)と同様に、p型チャンネルのMOSFET(PMOS)も作ることができ、NMOSとPMOSを組み合わせた「CMOS」(Complementary MOS:相補型MOS)は、現在の論理回路の重要技術です。

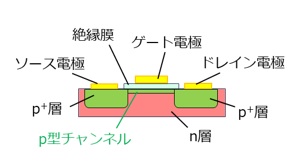

PMOSは図8のような構造です。ゲート電極に、ソース電極に対してマイナスの電圧をかけることによって、絶縁膜との境界部分のn層を、p型に変えることでp型チャンネルを作ります。

【図8 p型チャンネルMOSFET断面図】

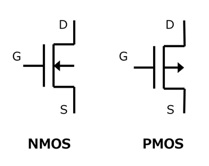

MOSFETの回路記号は、図9のようなものが一般的で、矢印はp型層からn型層に向かっています。

【図9 MOSFETの回路記号(NMOSとPMOS)】

NMOSはゲートをソース(およびドレイン)よりプラスの電位にするとp型層のゲート界面にn型チャンネルができて導通し、PMOSはゲートをソース(およびドレイン)よりマイナスの電位にするとn型層のゲート界面にp型チャンネルができて導通します。

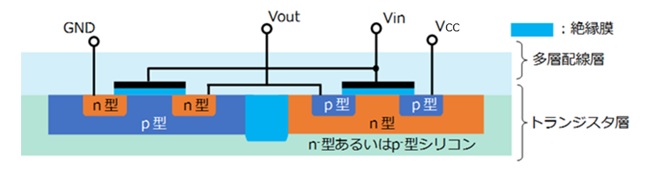

CMOSはNMOSとPMOSを並べて半導体ウェハに作りこみます。

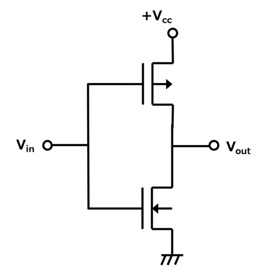

例えば図10のように結線したものでは、Vin=Vcc(正の電圧)の時、NMOSにはn型チャンネルができますが、PMOSにはp型チャンネルはできません。従って、Voutはグランドと同電位(ゼロ)になります。

Vinがグランドと同電位(ゼロ)の時、PMOSにはp型チャンネルができますがNMOSにはn型チャンネルはできません。従って、VoutはVccと同電位になります。

このようにVoutはVinと反対の動きをするので、この回路を「インバータ」と言います。

CMOSでは、この回路のようにどちらかのMOSが導通しない状態になっているので、信号が切り替わる一瞬を除いて電流が流れないため消費電力が少なくて済むのが一番のメリットです。

【図10 CMOSを用いたインバータ】

図11は、半導体ウェハに作りこまれたCMOSの構造概念図で、左側がNMOS、右側がPMOSです。

【図11 CMOSの構造概念図】

3.JFET(Junction FET)とは?

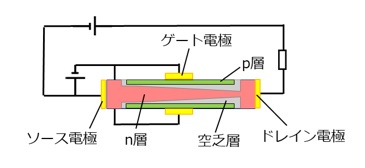

MOSFETのようにゲート界面に伝導型を変える反転層を作るわけではありませんが、ゲート界面の空乏層厚さを変えて電流を制御するタイプの電界効果トランジスタがあります。

図12のようにn型半導体をp型半導体で挟んだような構造で、ゲートに負の電圧を与えるとpn接合が逆バイアスとなるため空乏層が広がって、ソースからドレインに向かう電子の通り路が狭まって電流が制限されます。つまりゲート電圧を変えることでドレイン電流を変えることができるわけです。

ゲートにpn接合(pn junction)を利用しているので「Junction FET」(JFET)と呼ばれます。

p層から延びる空乏層は、ドレイン側に行くほど厚くなります。

ドレイン電圧(Vds)を上げていくと上下の空乏層が接するようになりますので、 Vdsをそれ以上に上げてもドレイン電流はほとんど増えなくなります。

【図12 JFETの構造概念図】

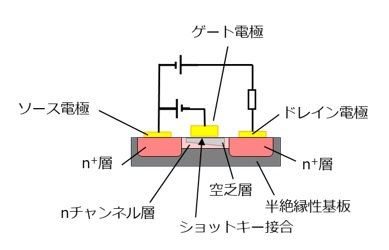

4.MESFET(Metal Semiconductor FET)とは?

GaAs等の良質な半絶縁性基板が得られる半導体では、図13のように半絶縁性基板の上にnチャンネル層を形成し、この層に適当なショットキー障壁を作る金属を接合してゲート電極にすれば、ゲートに逆バイアス電圧をかけることで空乏層の幅を変え、ドレイン電流を変えることができます。

MES(MEtal-Semiconductor)構造をゲートに用いているので「MESFET」と呼ばれます。

ゲートから延びる空乏層は、ドレイン側に行くほど厚くなります。

ドレイン電圧(Vds)を上げていくと空乏層が半絶縁層に接するようになりますので、 Vdsをそれ以上に上げてもドレイン電流はほとんど増えなくなります。

【図13 MESFETの構造概念図】

5.連載「これならわかる半導体超入門」の終わりに

半導体デバイスは一部の例外(ホール素子などのセンサーが主)を除いて、n型半導体とp型半導体、あるいは半導体と金属、絶縁体との界面(接合面)付近で起こる現象を利用しています。

そのため、デバイスについて深く知るためには、接合部分で何が起こっているのか、接合部を流れる電流はどのような挙動を取るのか、さらには接合部を組み合わせると何が起こるのかという点を整理して理解することが必要です。

そこでこの連載コラム「これならわかる半導体超入門」では、材料としての半導体の性質から始めて様々な接合部と、その性質を使ったディスクリートデバイスの説明をしてきました。

この先さらにIC(Integrated Circuit:集積回路)の動作を理解するためには、このコラムでは説明しなかった接合部の容量等の知識も必要です。また、電動自動車の普及などによって最近注目を集めているパワー半導体についてもこのコラムでは触れていません。

しかし、このコラムで何度も説明に使ったバンド構造を頭に思い描くことができれば、大概の半導体デバイスの原理は理解することができます。

(アイアール技術者教育研究所 H・N)