3次元積層チップのテスト技術とテスト容易化設計【提携セミナー】

半導体・電子部品実装 研究・開発 生産技術・品質保証 専門技術・ノウハウ

3次元積層チップのテスト技術とテスト容易化設計【提携セミナー】

| 開催日時 | 未定 |

|---|---|

| 担当講師 | 四柳 浩之 氏 |

| 開催場所 | 未定 |

| 定員 | 未定 |

| 受講費 | 未定 |

★3D ICチップの製造・実装時に発生する欠陥や故障事例とその検出手法

複雑化するチップ構造に対応する“高信頼性で高効率なテスト技術”

3次元積層チップのテスト技術とテスト容易化設計

【提携セミナー】

主催:株式会社技術情報協会

講座内容

微細化に加えて新たな高集積化技術として複数ICチップを重ねて実装する3次元積層チップが注目されている。3次元積層チップの製造では従来のICチップ単体のテストに加えて,接続に用いるシリコン貫通ビア(TSV)のテストや積層チップ間の接続テストなど複雑なテスト工程が必要となる。また,テストの高信頼化・効率化のためのテスト容易化設計が必須である。本講座では,3次元積層チップのテストに用いられるテスト技術やテスト容易化設計技術について解説する。

【本セミナーで学べること】

- 3次元積層チップの構造と利点について

- ICチップの製造時,実装時に発生する欠陥とそのテスト技術について

- ICチップのテスト容易化設計(DFT)の必要性と各種DFT技術について

- 3次元積層チップに固有のテスト技術・DFT技術について

担当講師

徳島大学 大学院社会産業理工学研究部 教授 博士(工学) 四柳 浩之 氏

セミナープログラム(予定)

1.3次元積層チップの概要

1.1 なぜICチップを積層するか

1.2 3D, 2.5D, チップレット実装

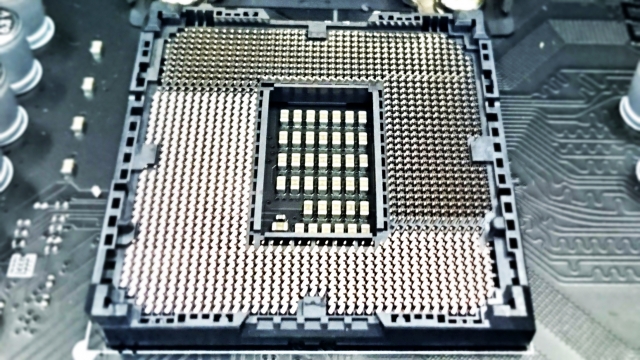

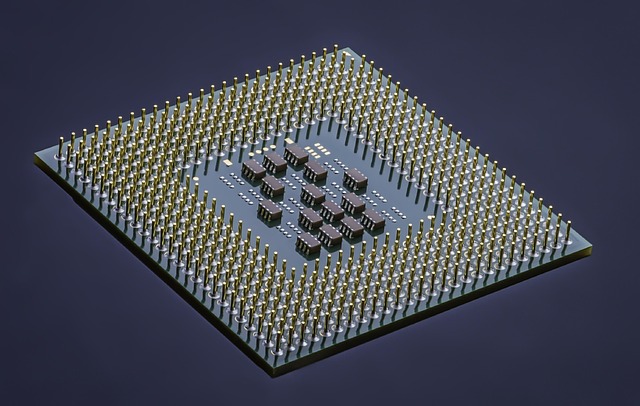

1.3 チップ間の接続:シリコン貫通ビア(TSV), マイクロバンプ, インターポーザ

1.4 チップの積層工程

2.3次元積層チップのテスト技術

2.1 ICチップのテストとは

2.2 欠陥と故障モデル

2.3 ICチップ内部およびICチップ間接続のテスト技術

2.4 チップ積層時のテスト工程

3.3次元積層チップのテスト容易化設計

3.1 テスト容易とは

3.2 代表的なテスト容易化設計(DFT)

3.2.1 スキャン設計

3.2.2 バウンダリスキャン

3.2.3 BIST

3.2.4 テストポイント挿入

3.3 3次元積層チップ向けのテスト容易化設計

3.4 高信頼化へ向けてのテスト容易化設計

4.まとめ

【質疑応答】

公開セミナーの次回開催予定

開催日

未定

開催場所

未定

受講料

未定

備考

資料は事前に紙で郵送いたします。

お申し込み方法

★下のセミナー参加申込ボタンより、必要事項をご記入の上お申し込みください。

★【LIVE配信】、【アーカイブ配信】のどちらかご希望される受講形態をメッセージ欄に明記してください。

※お申込後はキャンセルできませんのでご注意ください。

※申し込み人数が開催人数に満たない場合など、状況により中止させていただくことがございます。