【早わかり電子回路】レジスタ回路とシフトレジスタ回路

今回は、デジタル回路のうち「レジスタ回路」「シフトレジスタ回路」について説明します。

1.レジスタ回路/シフトレジスタ回路とは?

「レジスタ回路」は記憶装置を構成します。

また、レジスタ回路に適当な論理回路を付加して、シフトパルスがくるごとに記憶内容が右または左に1つずつ移動するようにしたものを「シフトレジスタ回路」といいます。

基本となる素子としてフリップフロップが多く用いられます。

2.レジスタ回路の基本

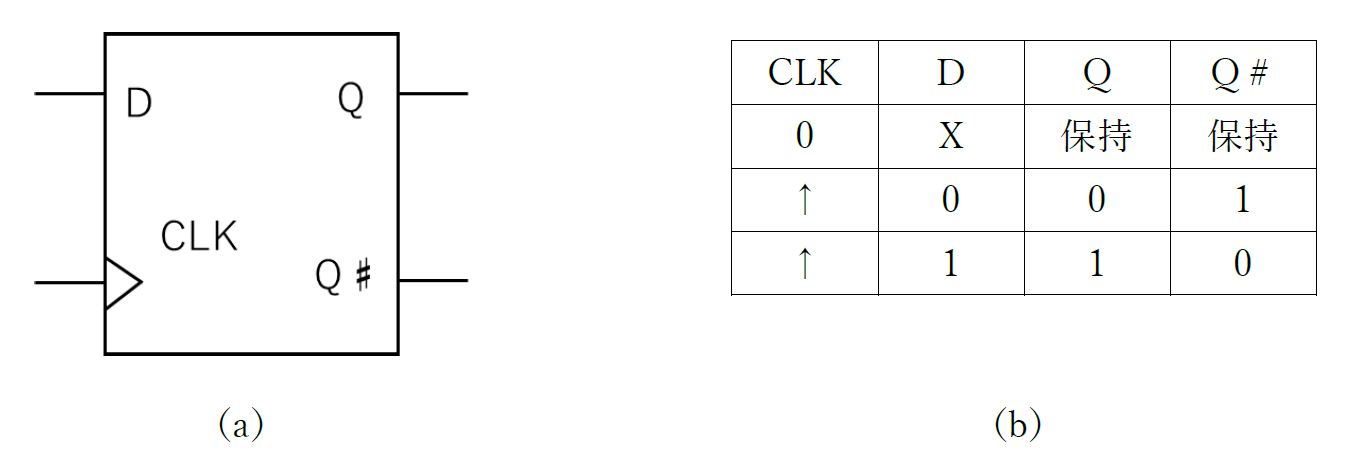

図1は、当連載の順序回路の解説の回で示したことがある、クロック(CLK)を入力するようにしたDフリップフロップの(a)図記号と(b)真理値表です。

【図1 Dフリップフロップの図記号と真理値表の例】

図1(b)において、CLKの↑は、クロック波形の立ち上がりを示し、このタイミングでDの値を取り込み、Qから出力します。DのXはどちらの入力でもよいことを表し、CLKが0の時は、どちらの入力でもそのまま保持されます。

このように、クロック波形の立ち上がりで、Dの値を取り込み、Qから出力することは、Dの値を記憶することになります。

実は、このDフリップフロップが、そのままレジスタ回路として用いることができます。

機能としては、データを一時的に記憶しておくということが挙げられます。

3.シフトレジスタ回路の基本

レジスタを並べてデータを扱う回路に「シフトレジスタ回路」があります。

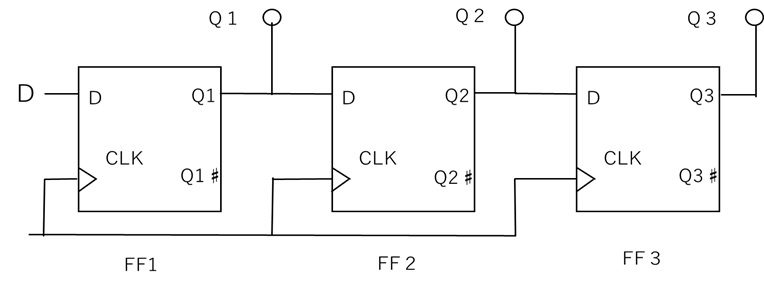

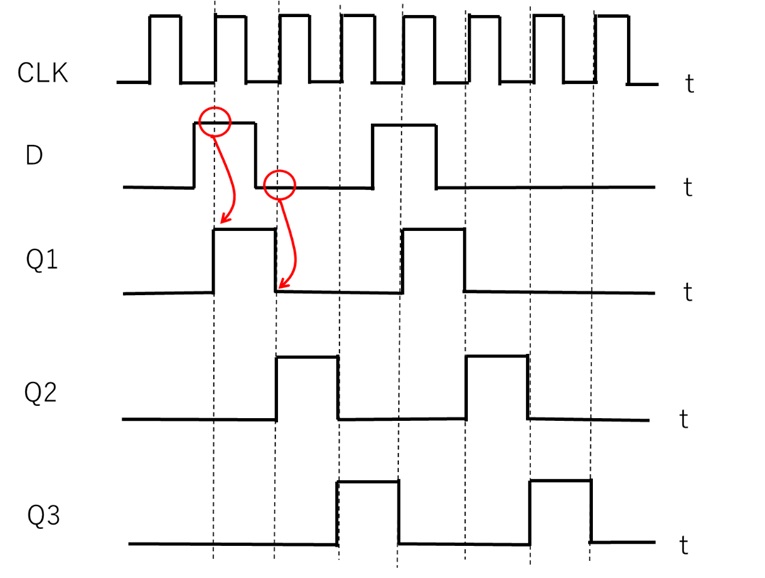

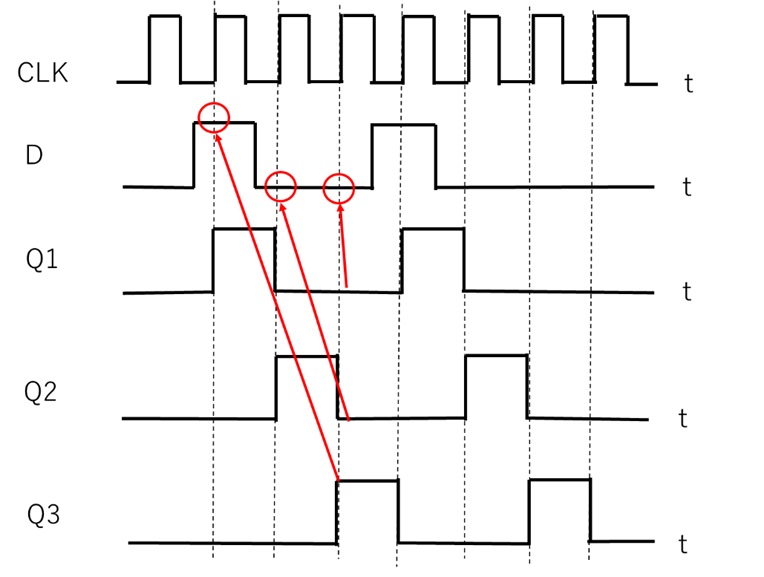

図2は、Dフリップフロップを3つ接続した場合のシフトレジスタ回路を示し、図3は、そのシフトレジスタ回路のタイムチャートを示しています。

図2のように、フリップフロップを縦続に接続することをカスケード接続といいます。

【図2 Dフリップフロップを3つ接続したシフトレジスタ回路】

【図3 シフトレジスタ回路のタイムチャート】

図2のシフトレジスタ回路に、図3のCLKとDのパルスを入力すると、FF1の出力Q1には、図3のQ1のようなパルスが出力されます。これは、CLKの立ち上がりでDのパルスの値をとらえているためです(図3の赤色の部分)。

そして、FF2にFF1の出力Q1が入力されると、CLKのタイミングで、Q2が出力されます。(CLKの立ち上がる直前の値をとらえ、CLKが立ち上がった直後に出力しています。)

同様にしてQ3が出力され、クロック信号(CLK)に同期して入力するデータが順に移動(シフト)していることがわかります。

シフトレジスタは、シフト演算を行う回路だけでなく、遅延回路、シリアル-パラレル変換回路、パラレル-シリアル変換回路などに多く用いられています。

4.シフトレジスタ回路の応用(シリアル-パラレル変換回路)

シフトレジスタ回路の応用として、「シリアル-パラレル変換回路」を取り上げます。

データが、直列に並んでいることを「シリアル」、並列に並んでいることを「パラレル」といいます。

シリアルデータは、データを時系列上に展開したものです。

入力や出力の端子が各1つで済みますが、同じ量のデータを転送するのに時間がかかります。

パラレルデータは、データ幅分の全データを同時に入力または出力することができます。

ただし、入力や出力にデータ幅分の端子数が必要になります。

シリアル-パラレル変換の仕組み

ここで、図2のシフトレジスタ回路について見てみると、Q1、Q2、Q3の各端子はデータがシフトしていきますが、同じCLKの時には、例えばQ3には2つ前のCLKのDのデータが現れ、Q2には1つ前のCLKのDのデータが現れ、Q1には同じCLKのDのデータが現れることになります。

すなわち、DのデータがQ1、Q2、Q3に残っていることになるので、Q1、Q2、Q3を同時に出力すると、シリアルに入力されたDのデータが、一度に(パラレルに)出力されることになります。

これで、シリアル-パラレル変換されたことになります。

図4のタイムチャートにその様子を示しました。(赤色の部分)

従って、図2は、シリアル-パラレル変換回路としても用いられることになります。

【図4 シリアル-パラレル変換回路のタイムチャート】

[シリアル⇔パラレル]の変換の重要性

最近では、高速通信が可能になり、装置間の通信においては省配線化のためにシリアル通信が多く用いられています。

例えば、パソコンのUSB(Universal Serial Bus)などがシリアル通信の代表と言えるでしょう。

ただ、装置の内部では、データを高速で大量に処理するためにパラレルデータが用いられることが多いです。

従って、シリアル-パラレル変換回路や、その逆のパラレル-シリアル変換回路は、とても重要になります。

その基となるシフトレジスタ回路も、ほとんどの装置で使用されていると言ってもよいでしょう。

(日本アイアール株式会社 特許調査部 E・N)

](https://engineer-education.com/wp/wp-content/uploads/2021/10/Circuit-element0-150x150.png)

](https://engineer-education.com/wp/wp-content/uploads/2022/08/elearning_AC-circuit1_0-150x150.png)