【パワー半導体の基礎】パワーMOSFETの動作原理|オフ状態とオン状態、寄生抵抗などを解説

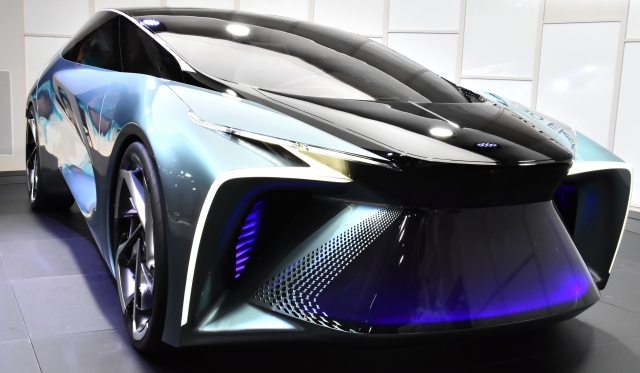

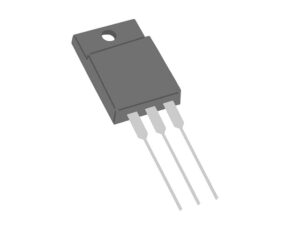

「パワーMOSFET」(metal-oxide-semiconductor field-effect transistor)と呼ばれているパワー半導体デバイスは、高電圧・高電流を扱う電気回路のスイッチとして不可欠であり、電気自動車、電車、発電・送電システム、各種産業機械、家庭用電化製品、音響機器などのために、耐圧、駆動電流、スイッチング速度などの特性が異なる様々な製品が設計・製造されています。

この記事では、パワーMOSFETの基本的な動作原理を紹介します。

1.微細MOSFETとパワーMOSFETの違い

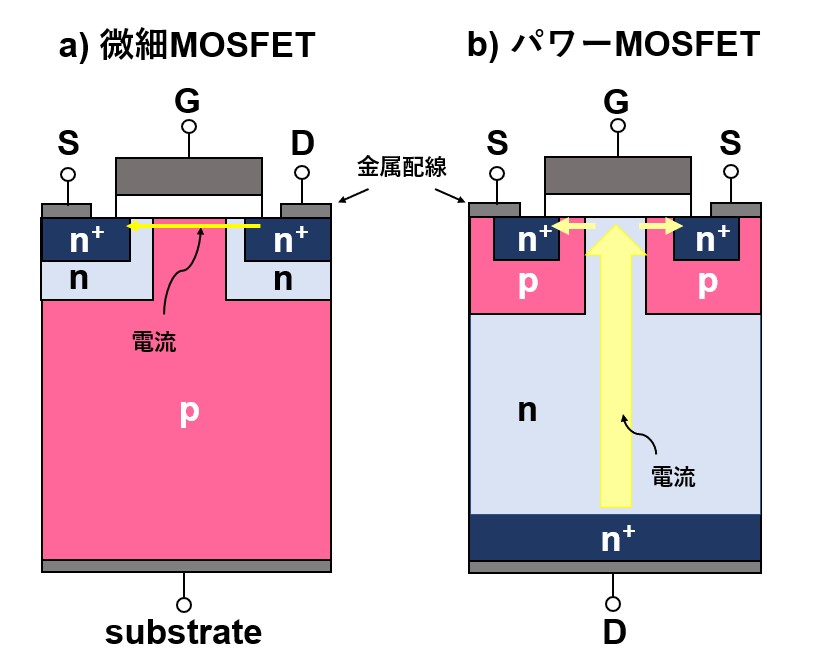

低電圧・低電流で動作するIC(integrated circuit)やLSI(large scale integration、大規模集積回路)の構成要素である微細なMOSFETでは、電流はシリコン(Si)基板の表面近傍(厚さ約0.1μm以下)を横方向に流れますが、高電圧・高電流用パワーMOSFETでは、ICやLSIよりも遥かに大きな電流がSi基板の底から表面に向かって流れます(図1参照)*1。

両者にはこのような大きな違いがありますが、基本的な動作原理は全く同じで、MOSFETのオン・オフ(スイッチング)は、ゲート電極に印加する電圧のオン・オフによって行います。

*1 耐圧が数10V以下の用途にはDMOS(double-diffused metal-oxide semiconductor)という横型のパワーMOSFETも用いられています。

【図1 微細MOSFETとパワーMOSFETの違い】

(図中のG、S、Dは、それぞれ、ゲート、ソース、ドレインの略。)

パワーMOSFETのドレイン側(基板の多くの部分)は、低濃度のn型領域になっています。低濃度n型領域を形成する目的は、ドレインに高電圧を印加した時に形成される「ドレイン空乏層によって耐圧を確保する」ためですが、パワーMOSFETに要求される耐圧は非常に高いため、n型領域の厚さは数10~数100μmになります。(Si基板の直径や厚さは業界で標準化されており、直径が6、8、12インチの基板の厚さはそれぞれ625、725、775μmです。)

2.MOSFETのオフ状態

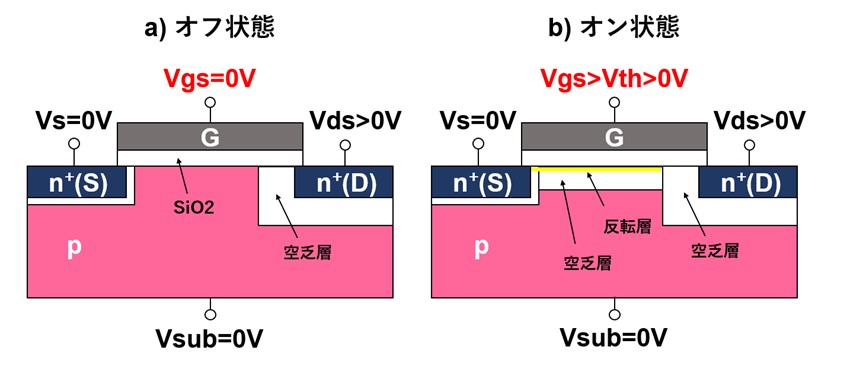

n+型のソースとp型領域を接地して(Vs=0V、Vsub=0V)、ドレイン電圧Vds(>0V)を印加しても、ゲート電圧Vgsが0Vの時は、MOSFETは「オフ状態」にあって電流は流れません。

電流が流れないのは、ソース側にあるn+p接合の接合障壁が、ソースからp領域への電子の流入を阻止しているからです(図2a参照)。

【図2 MOSFETのオン・オフ状態】

3.MOSFETのオン状態

一方、ゲート電圧Vgs(>0V)が上昇すると、ソース・ドレインの間にあるp型領域とゲート絶縁膜との界面近傍では、p型領域のホール(正孔)が基板の底面方向に押し出されて空乏化し、同時にp型領域に存在する少数の電子が界面近傍に引き寄せられます(図2b参照)。

反転層の形成

ゲート電圧が(p型領域の不純物濃度に依存する)ある値Vth(threshold voltage、閾値)以上になると、界面近傍に引き寄せられた「電子の濃度」がp型領域に元々存在していた「ホールの濃度」よりも遥かに高くなり、正負が反転してn+型になった薄い層「反転層」が形成されます(図2b参照)。反転層の厚さは、概ね100Å以下です。

「反転層」が形成された状態のことを、ソース・ドレイン間に「チャネル」が形成されたと表現します。「チャネル」(channel)は元来「水路、水の経路」という意味ですが、転じて「電子の通路」という意味で使われています。

ソース接合障壁の制御

反転層が形成された状態になると、ソース側のn+p接合の上記界面近傍の接合障壁が消滅するため、ソースから反転層に向かって大量の電子が流入し、これらの電子はドレイン電圧Vds>0Vに引き寄せられ、厚さが非常に薄い「チャネル」を通ってドレインに向かって一気に流れます(図2b参照)。これが「オン状態」です。(注:電子と電流は、流れる方向が逆向きです。)

このようにしてMOSFETでは、ゲート電圧のオン・オフによって「反転層」と「ソース接合の接合障壁の高さ」を制御することによって、n+ソースからp型領域に流入する電子の数を制御しています。このメカニズムは、パワーMOSFETでも全く同じです。

4.パワーMOSFETの寄生抵抗

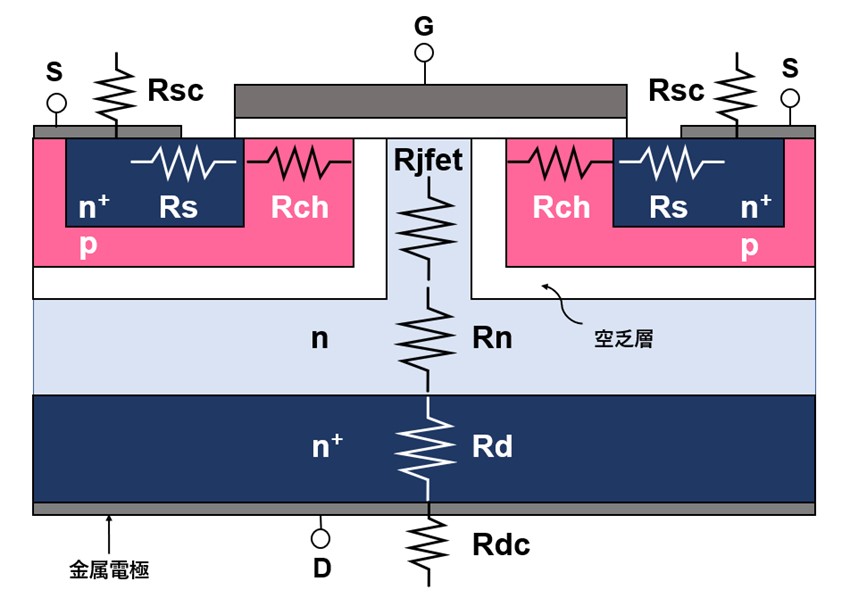

オン状態で流れる電流(電子の流れ)は、デバイスの構造に起因する幾つかの寄生抵抗成分の影響を受けます。

全寄生抵抗は、電極金属とソース・ドレインの接触抵抗(RscとRdc)、ソース・ドレインn+拡散層の抵抗(RsとRd)、チャネルの抵抗Rch、そしてn型領域の抵抗(RjfetとRn)の合計になります(図3参照)。

【図3 パワーMOSFETの寄生抵抗】

特に、RjfetとRnはパワーMOSFETに固有の寄生抵抗成分で、Rjfetは「JFET効果」という現象に起因する寄生抵抗です。

「JFET効果」とは、p型領域とn型領域の界面の横方向に広がる空乏層によってp型領域とp型領域の間にあるn型領域の幅(電子の通路の幅)が狭くなり、この部分の寄生抵抗が増加してしまうという現象で、JFET(junction FET)という半導体デバイスのオン・オフ動作の原理に似ているため(詳細割愛)、このように呼ばれています。この空乏層の幅と電子の通路の幅は、n型領域の不純物濃度に依存します。

そして、このJFET効果の影響で、パワーMOSFETの横方向の微細化には限界が存在します。

5.電子走行距離の定量的イメージ

低電圧・低電流を扱うLSIの微細なMOSFETでは、電子は基板表面に平行な方向に流れ、その経路の厚さは非常に薄いのですが(反転層の厚さは100Å以下、ソース・ドレイン拡散層の厚さは約0.1μm以下)、桁違いに大きな電流を流すパワーMOSFETでは、電子は基板表面のソースから基板底部のドレインに向かって(電流は基板の底から表面に向かって)遥かに広い領域(抵抗体の断面積が極めて大きい状態)を走行します(図1参照)。

一方、微細MOSFETのソース・ドレイン間距離は微細化の進展と共に急激に減少している(50nm以下)のに対して、パワーMOSFETのソース・ドレイン間距離は数100μmあり、n型領域やn+ドレイン拡散層の厚さが厚いため(抵抗体の長さが非常に長い状態)、これらの寄生抵抗は無視できない大きさになります。これらの抵抗は電流駆動能力に強く影響するので、デバイス構造やn型領域の不純物濃度などの設計には様々な工夫が盛り込まれています。

次回は、空乏層幅の不純物濃度依存性など、パワーMOSFETの空乏層について解説いたします。

(日本アイアール株式会社 特許調査部 A・Y)