3分でわかる技術の超キホン 集積回路(IC)とは?概要/分類/製造工程などを要点解説

今回は集積回路(IC: Integrated Circuit)についてお話したいと思います。

日頃使用している電気製品のほとんどには、機能を制御する電気回路の基板が入っています。

この基板上には、CPU(Central Processing Unit:中央演算処理装置)、RAM(Random Access Memory)やROM(Read Only Memory)等のメモリーに代表される集積回路や様々な周辺機能を有する集積回路、トランジスタやダイオード等の能動素子、抵抗やコンデンサ、インダクタ等の受動素子などで構成されています。

このコラムでは、一般的に「IC」と呼ばれる集積回路に焦点をあてて説明します。

1.集積回路(IC)とは?

集積回路は、一言でいうと主にシリコンウエハー(シリコンは珪素)の上にトランジスタやダイオード、抵抗、コンデンサなどの機能を持つ素子を多数に作り込んで配線接続したものです。

1950年代から欧米で開発が進み製品化されて現在に至っています。

回路規模である集積する素子の数により、SSI(Small Scale Integration)、MSI(Middle Scale Integration)、LSI(Large Scale Integration)に分けられます。

そして現在では、このLSIの分野でさらに大規模化が進み、VLSI(Very Large Scale Integration)、ULSI(Ultra-Large Scale Integration)、GSI(Giga Scale Integration)などと呼ばれるものまで出てきています。ちなみにGSIでは、素子数が10億以上ともいわれています。

また、これらの一つの機能を実現する集積回路であるチップ(「ダイ」とも呼ぶ)を複数種類集めてシステムとして集積化するSOC(System On a Chip)などの製品も出ています。

2.集積回路(IC)ができるまで

ここでは、集積回路製造の工程を以下に説明します。

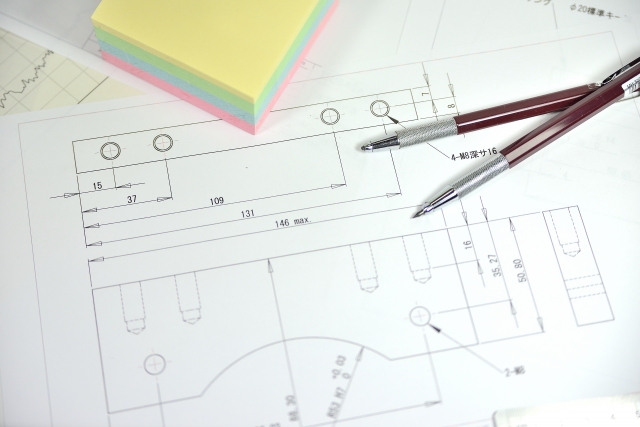

(1)回路設計/レイアウト設計

最初に集積回路の機能を実現するための回路設計を行います。

設計後シミュレーションなどを経て、能動素子・受動素子の部品配置であるレイアウト設計に入ります。

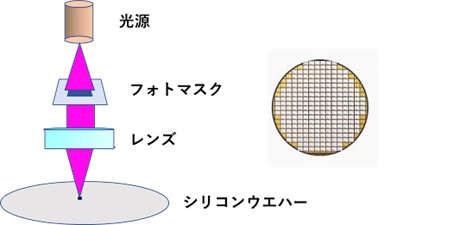

レイアウト設計後、次にフォトマスク(石英ガラスなど)基板上に「フォトマスク」を作成します。

これは、シリコンウエハーに焼き付けるための原版で、素子の積層ごとに作成され複数枚で構成されます。

(2)前工程

「前工程」は、集積回路のチップの作成工程です。

集積回路のチップのベースとなる「シリコンウエハー」は、高純度化された多結晶シリコンより超高純度化された単結晶シリコン(インゴット)を作成して薄く切断(厚さ1mm程度)して作成されます。

シリコンウエハーのサイズは、一般的に200mmφ、300mmφが使用されます。

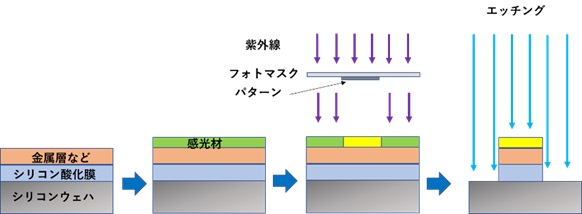

このシリコンウエハーに、以下の成膜工程、感光材塗布工程、露光工程、現像工程、エッチング工程、レジスト剥離工程などから構成されます。

- 成膜工程:ICを作るための素材となる酸化シリコン膜、窒化シリコン膜、金属薄膜などの膜を形成していきます。

- パターン転写工程:成膜後に、シリコンウエハー上にフォトマスクを利用してパターンを焼付ける為に予め感光材(フォトレジスト)を塗布します。次に光源より紫外線の照射がフォトマスクを通してシリコンウエハーに到達します。露光/現像を行う工程です。

- エッチング工程:パターン転写後にシリコンウエハーの表面加工を行う工程で、配線などの形状を作成します。

- レジスト剥離工程:エッチング後不要となった感光材を取り除き、シリコンウエハーに残る不純物を除去します。

(3)後工程

「後工程」は、各チップをそれぞれパッケージングする工程です。

- プローブ検査工程:チップの一つ一つを通電検査して性能の可否を行います。

- ダイシング:シリコンウエハー上のダイと呼ばれる各チップをダイシングソーで切り出します。

- パッケージング:チップをリードフレームに固定して、金属ワイヤで配線を行い外部への端子を出します。その後セラミックやエポキシ樹脂などで封止を行いリードフレームから切り取ります。

- 最終検査:出来上がった集積回路をテスターによる最終検査を行います。特性検査・外観検査・信頼性検査を経て合格品を選別します。

3.集積回路(IC)の分類

(1)モノリシックとハイブリッド

集積回路には、その構造により「モノリシック」と「ハイブリッド」に分けられます。

「モノリシック」とは、その名の通り一つの基板上に、トランジスタ、ダイオード、抵抗、コンデンサなどを作りこんで一体化したものです。

通常ICとはこのモノリシックICを示します。論理回路、メモリー回路など広く利用されます。

これに対して「ハイブリッド」は、基板に絶縁体を用いたもので、この基板上にモノリシックICやトランジスタ、ダイオードなどの半導体素子、抵抗、コンデンサなどを高密度に配置したパッケージしたものです。

比較的に小型化が可能で高周波回路、大電力の下での利用に適しています。

(2)アナログ集積回路とデジタル集積回路

集積回路の種類には、「アナログ集積回路」と「デジタル集積回路」という分け方もあります。

「アナログ集積回路」では、連続的な波形の変化であるアナログ信号を扱うもので、「オペアンプ」と言われる演算増幅回路が代表的なアナログ集積回路です。

そのほかにもパワーアンプ、AC/DCコンバータ、DC/ACコンバータなど電源回路に使用される集積回路が挙げられます。

「デジタル集積回路」では、アナログ信号を標本化した離散信号であるデジタル信号を扱うもので、論理集積回路・メモリー回路・マイクロプロセッサなど挙げられます。また「ASIC」(Application Specific Integrated Circuit)と呼ばれる特定用途向け集積回路もメーカーなどでカスタマイズして多く利用されています。

4.微細加工技術の粋を集めた集積回路(IC)の世界

集積回路に関して、集積規模による分類や製造工程も含め流れを説明してきました。

集積回路は、時代とともに高集積化が進み、文中にもありましたGSIという素子数が10億個という規模の製品があります。

集積回路の製造は、微細加工技術の粋を集めて作られています。

このため、例えば一つのシリコンウエハー上に多数のチップを形成していますが、良品の割合である「歩留まり」が重要となり、この歩留まりの向上が常に求められます。一方で大量生産化と集積度の増大によるチップの大型化に応えるため、シリコンウエハーサイズでは450mmφの開発も進んでいます。

また集積回路の製造にあたっては、シリコンウエハーのインゴットを作る素材メーカー、半導体製造装置を製造するメーカー、この製造ツールを利用して半導体メーカーが集積回路の製品を製造しています。

またこの背景には、チップのレベルやパッケージング後のレベルでのテストを行うテスターメーカーに支えられています。さらにこのチップを利用して回路基板を作成し、電気製品を作る機器メーカーへと半導体産業のすそ野が広がっています。

(日本アイアール株式会社 特許調査部 T・T)

](https://engineer-education.com/wp/wp-content/uploads/2021/10/Circuit-element0-150x150.png)