先端パッケージにおける実装技術・実装材料・冷却技術の最新動向とハイブリット接合技術【提携セミナー】

先端パッケージにおける実装技術・実装材料・冷却技術の最新動向とハイブリット接合技術【提携セミナー】

おすすめのセミナー情報

もっと見る| 開催日時 | 2024/8/2(金)13:00~16:30 |

|---|---|

| 担当講師 | 川野 連也 氏 |

| 開催場所 | 【WEB限定セミナー】※会社やご自宅でご受講下さい。 |

| 定員 | - |

| 受講費 | 通常申込:49,500円 E-Mail案内登録価格 46,970円 |

先端パッケージにおける

実装技術・実装材料・冷却技術の

最新動向とハイブリット接合技術

《2.5D/3D異種機能集積(チップレット)を実現するパッケージ形態》

《ハイブリッド接合とそのプロセス・課題、最先端実装に要求される材料・冷却技術》

【ECTC2024などの最新情報も交えながら解説】

【提携セミナー】

主催:サイエンス&テクノロジー株式会社

受講可能な形式:【Live配信(アーカイブ配信付)】のみ

高密度実装を必要とするアプリケーション、チップレットを実現する2.xD/2.5D/3D集積技術、高密度実装のカギとなるハイブリッド接合のプロセスと課題および装置の開発状況、熱界面材料(TIM)やアンダーフィル材料などの要求される材料技術、半導体パッケージの冷却技術の概要、生成AIなどの大規模計算システムで要求される冷却技術などについて、最新情報とともに解説します。

セミナー趣旨

半導体回路の微細化は数十年に渡り、半導体デバイスの高集積化、低消費電力化、低コスト化を同時にもたらしてきたが、このような従来のスケーリングには限界が来ている。特に先端デバイスの設計コストが1製品100億円を超えたり、本来のトランジスタ性能を活かすことができず放熱でシステム性能が決められる時代が来ている。このような状況にあっても、実装におけるスケーリングの余地はまだまだ大きい。特に異なるプロセスや既存チップを組み合わせるチップレットの広がりによって、高密度実装への期待は拡大し、実装への要求内容も急速に変化している。

本講座ではこのような高密度実装技術を俯瞰し、さらなる高性能・多機能を実現する実装技術、実装材料技術および冷却技術について、世界最大の実装学会であるECTC2024などの最新情報も交えながら解説を行う。

得られる知識

- 先端パッケージの必要性とそれを実現するための技術の将来予測

- 三次元ICのための高密度実装を必要とするアプリケーション

- 高密度実装技術を実現するパッケージ形態とそれぞれの得失

- 高密度実装のカギとなるハイブリッド接合技術、プロセス課題や装置開発状況

- 先端パッケージに要求される実装材料技術

- 熱マネジメントが性能を決める生成AIなどの大規模計算システムで要求される冷却技術

受講対象

半導体製造、組立&テスト、製造装置、実装材料の各メーカー、半導体プロセス・実装分野での研究開発・製造に携わる方(初心者から中級者まで)

担当講師

東京大学 システムデザイン研究センター(d.lab) 特任研究員 博士(工学) 川野 連也 氏

専門:高密度半導体実装技術、三次元実装技術

1989年3月 大阪大学大学院工学研究科修士課程修了、2008年9月 東京工業大学大学院総合理工学研究科博士後期課程修了。1989年 日本電気株式会社に入社。裏面照射型赤外線イメージセンサ、Cu/Low-k配線、積層DRAM、FOWLP等の先端実装の研究開発に従事。NECエレクトロニクス、ルネサスエレクトロニクスを経て、2011年 EV Group Japanに入社。技術部門長として接合技術等のソリューション提供を統括。2015年シンガポール国立研究所のIMEにシニアサイエンティストとして着任。FOWLP、ハイブリッドボンディングなどの国際連携コンソーシアムをプロジェクトリーダーとして遂行。2022年1月より東京大学に着任、三次元実装技術、先端実装材料の研究を担当、現在に至る。

研究室のホームページ: http://www.dlab.t.u-tokyo.ac.jp/

セミナープログラム(予定)

1.はじめに -高密度実装の必要性-

1.1 パッケージ配線スケーリングと配線ギャップ

1.2 先端パッケージの変遷

1.3 各種高密度パッケージの優劣比較

1.4 配線密度向上およびパッケージ大型化の技術トレンド

1.5 チップレット解説

1.6 設計・デバイス・プロセス・実装の全体最適化(DTCO/STCO)

2.高密度実装技術のアプリケーション

2.1 2nmテクノロジーノード以降のデイバス構造およびパッケージ構造の変化

2.2 高密度実装を要求するロジックアプリケーションとその要求仕様

2.3 高密度実装を要求するメモリアプリケーションとその要求仕様

2.4 高密度実装を要求するイメージセンサアプリケーションとその要求仕様

3.2.5D/3D異種機能集積(チップレット)を実現するパッケージ形態とベンチマーク

3.1 Siインターポーザーを用いた2.5D/3D集積技術

3.2 Siブリッジを用いた2.xD/3D集積技術

3.3 高密度配線基板を用いた2.xD/3D集積技術

3.4 光電融合を実現する2.xD/3D集積技術

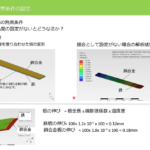

4.高密度実装のカギとなるハイブリッド接合技術およびそのプロセス課題

4.1 ハイブリッド接合のメカニズム

4.2 ウェハレベルハイブリッド接合のプロセスフローと課題

4.3 ハイブリッド接合に必要な検査工程

4.4 チップレベルハイブリッド接合のプロセスフローとその課題

4.5 高歩留まりハイブリッド接合を実現するためのプロセス技術

5.高密度実装に要求される材料技術

5.1 放熱効率を支配する熱界面材料(TIM)

5.2 狭ピッチバンプ接続のカギとなるアンダーフィル材料

5.3 高速信号伝送、低反りを実現する層間絶縁膜材料・基板材料

5.4 低温ハイブリッド接合を実現する銅めっき技術

6.最先端実装に要求される冷却技術

6.1 半導体パッケージの冷却技術概説

6.2 スーパーコンピューター富岳に使われる冷却技術

6.3 シリコンチップを直接冷却するオンチップ冷却技術

6.4 システム全体を冷却液に浸す液浸冷却技術

6.5 チップの内部に冷却液を入れて放熱するマイクロ流体冷却技術

□ 質疑応答 □

公開セミナーの次回開催予定

開催日

2024/8/2(金)13:00~16:30

開催場所

【WEB限定セミナー】※会社やご自宅でご受講下さい。

受講料

49,500円 ( E-Mail案内登録価格 46,970円 )

定価:本体45,000円+税4,500円

E-Mail案内登録価格:本体42,700円+税4,270円

E-Mail案内登録なら、2名同時申込みで1名分無料

2名で49,500円 (2名ともE-Mail案内登録必須/1名あたり定価半額24,750円)

※テレワーク応援キャンペーン(1名受講)【オンライン配信セミナー受講限定】

1名申込みの場合:受講料( 定価:37,400円/E-mail案内登録価格 35,640円 )

定価:本体34,000円+税3,400円

E-mail案内登録価格:本体32,400円+税3,240円

※1名様でオンライン配信セミナーを受講する場合、上記特別価格になります。

※お申込みフォームのメッセージ欄に【テレワーク応援キャンペーン希望】とご記載ください。

※他の割引は併用できません。

★【S&T会員登録】と【E-Mail案内登録】の詳細についてはこちらをご参照ください。

※E-Mail案内登録をご希望の方は、申込みフォームのメッセージ本文欄に「E-Mail案内登録希望」と記載してください。ご登録いただくと、今回のお申込みからE-mail案内登録価格が適用されます。

配布資料

PDFテキスト(印刷可・編集不可)

※開催2日前を目安に、主催者サイトのマイページよりダウンロード可となります。

備考

※講義中の録音・撮影はご遠慮ください。

※開催日の概ね1週間前を目安に、最少催行人数に達していない場合、セミナーを中止することがございます。

お申し込み方法

★下のセミナー参加申込ボタンより、必要事項をご記入の上お申し込みください。